# **Programmable Memory Controller for Vector System-on-Chip** Tassadaq Hussain

## **Problem-Formulation**

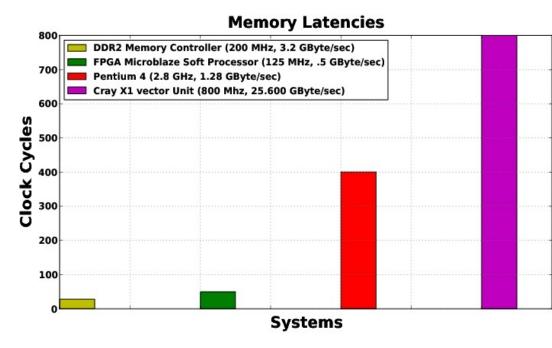

Wall Clock Time increases with the increase of memory size:

```

= Number of Cycle / Frequency of CPU

WCT

```

Number of Clocks are dependent:

- Computation Delay

- Address/Data Management Delay

- On-chip/Off-chip Bus Delay

- Memories Delay

## **Evaluation**

- **\***Software Compilation Framework

- GNU GCC 4.2.0

- **\*RTL** simulation

- Modelsim SE version 6.3c

- **\* FPGA CAD Software**

- Quartus II

- **\*** Hardware Platform

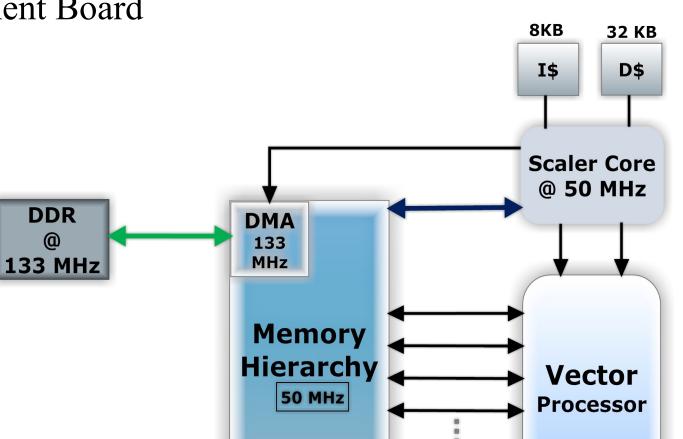

- AlteraDE4 Development Board

- **\*** Application Kernels

- Image Processing

- 2D Filter

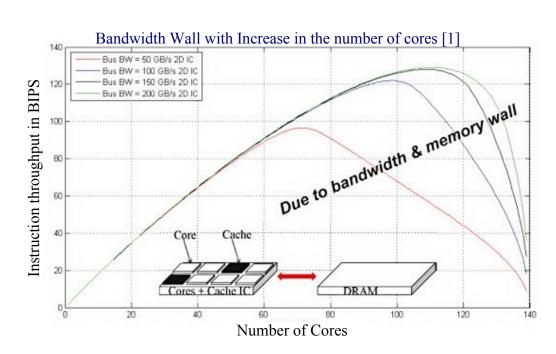

- \* Efficient memory hierarchy between the computing unit and the DRAM memory.

- \* Memory access policies, strided scatter/gather prefetchers.

- \* A programming model is required for the design

#### Proposal

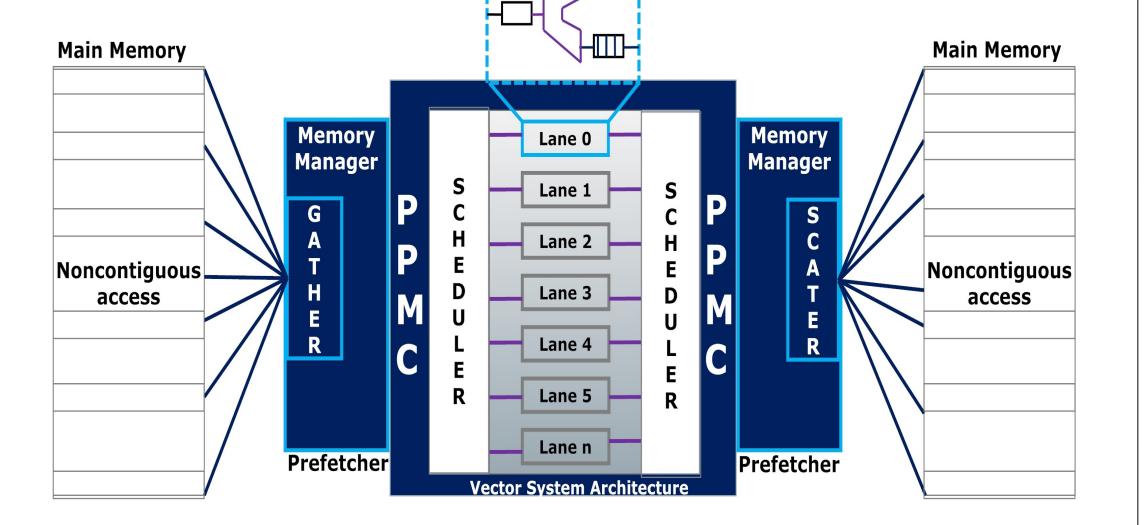

- As with conventional scalar processors, all classes of vector machine are required to have a Programmable Memory Controller which includes:

- Manage processing elements without the support of Master core.

- Intelligently schedules multiple data accesses from different threads.

- Efficiently prefetch complex/irregular patterns.

- Support standard C/C++ language calls to identify tasks ۹ in software.

- Combine all the functions into one chip the FPGA based system becomes smaller, faster, and consume less power.

## **Preliminary Results**

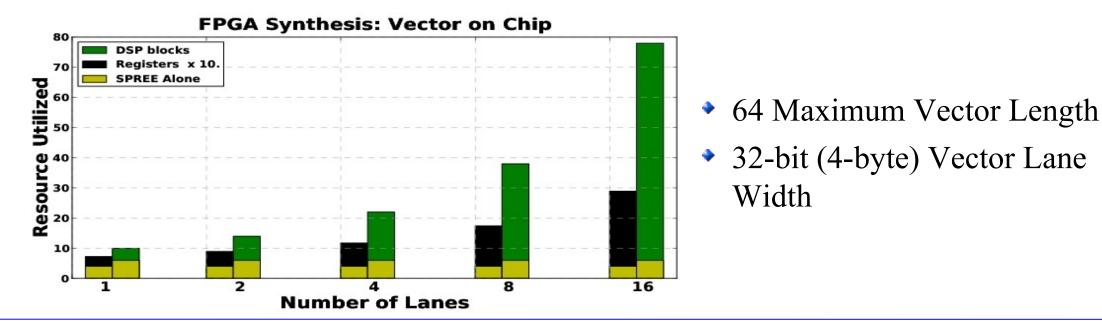

#### **Quratus II Synthesis Summary**

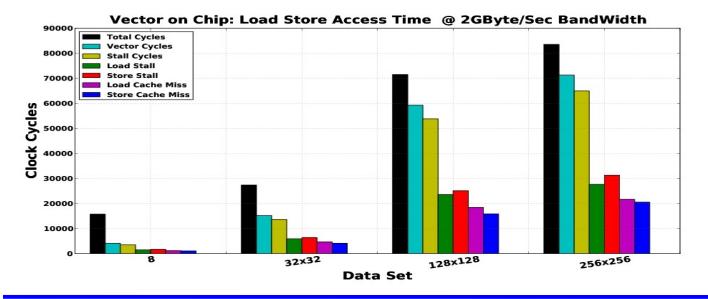

#### **Datasets Load/Store Time**

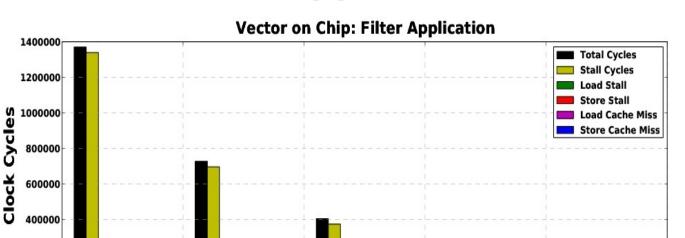

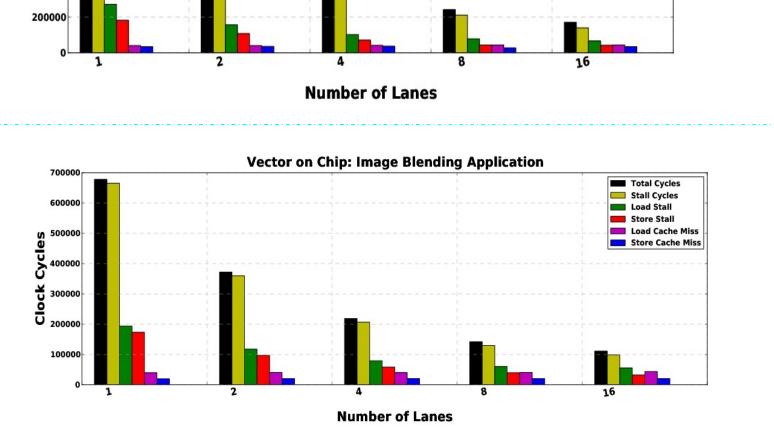

#### **Application Execution Time**

#### Contact emails: tassadaq.hussain@bsc.es

- Reconfigurable Memory Controller with Programmable Pattern Support. Hussain TASSADAQ, Miguel Pericas, Nacho Navarro, Eduard Ayguade. 5th HiPEAC Workshop on Reconfigurable Computing, WRC 2011.

- Implementation of a Reverse Time Migration Kernel using the HCE High Level Synthesis Tool Hussain TASSADAQ, Miquel Pericas, Nacho Navarro, Eduard Ayguade. The 2011 International Conference on Field-Programmable Technology FPT 2011 IIT Delhi New Delhi, India 12-14 December 2011

- PPMC : A Programmable Pattern based Memory Controller Hussain TASSADAQ, Muhammad Shafiq, Miguel Pericas, Nacho Navarro, Eduard Ayguade ARC 2012, the 8th International Symposium on Applied Reconfigurable Computing 21 - 23 March 2012 The Chinese University of Hong Kong, CUHK, Hong Kong

- PPMC : Hardware Scheduling and Memory Management support for Multi Hardware Accelerators Hussain TASSADAQ, Miquel Pericas, Nacho Navarro, Eduard Ayguade. FPL2012 | 22nd International Conference on Field Programmable Logic and Applications FPL2012 Oslo, Norway, Aug. 29-31, 2012.

#### [1] Muhammad Bakir; Georgia Tech.

### **Conclusions & future work**

In future, we are planning to embed a selective static/dynamic set of data access pattern inside Memory Controller for vector accelerator architecture that would effectively eliminate the requirement of programming system by the user for a range of applications.

Barcelona Supercomputing Center Centro Nacional de Supercomputación **BSC**~Microsoft Research Centre

Microsoft<sup>®</sup> Research