# MIPS-to-Verilog, Hardware Compilation for the eMIPS Processor

Karl Meier, Alessandro Forin Microsoft Research

September 2007

Technical Report MSR-TR-2007-128

Microsoft Research Microsoft Corporation One Microsoft Way Redmond, WA 98052

| - 1 | 2 - |  |

|-----|-----|--|

|-----|-----|--|

# MIPS-to-Verilog, Hardware Compilation for the eMIPS Processor

# Karl Meier, Alessandro Forin Microsoft Research

#### **Abstract**

The MIPS-to-Verilog (M2V) compiler translates blocks of MIPS machine code into a hardware design represented in Verilog. The design constitutes an Extension for the eMIPS processor, a dynamically extensible processor realized on the Virtex-4 XC4LX25 FPGA. The Extension interacts closely with the basic pipeline of the microprocessor and recognizes special Extension Instructions, instructions that are not part of the basic MIPS ISA. Each instruction is semantically equivalent to one or more blocks of MIPS code. The purpose of the M2V compiler is to automate the process of creating Extensions for the specific purpose of accelerating the execution of software programs.

M2V is a three-pass compiler that accepts as input basic blocks in the form generated by the eMIPS BB-Tools, a set of programs for the analysis and instrumentation of MIPS ELF images. Pass 1 of M2V generates a circuit graph that is semantically equivalent to the basic block that is being accelerated. Pass 2 schedules the operations in the circuit graph under the microarchitectural constraints of the eMIPS processor. Pass 3 emits synthesizable Verilog that constitutes the hardware accelerator that runs in the eMIPS extension slot.

The compiler was implemented from scratch in C++ and despite its current limitations it can already compile a few simple examples. The quality of the synthesizable Verilog that is generated by M2V compares favorably with hand-generated code for the same input. On a 64-bit division test M2V generates an Extension that performs at the same speed but uses half the area of the hand-generated version.

#### 1 Introduction

An embedded system typically runs a small set of applications and has tight power, cost, and performance criteria. Using a general purpose CPU for these systems can help meet the performance goals, but inefficiency can result when specialized resources, such as a floating point unit (FPU), are present but seldom, if ever, used. A lower power processor with a reduced instruction set

architecture (ISA) and without a FPU may suffer from poor performance.

Extensible processors try to compromise between general purpose CPUs and minimal RISC implementations. Extensible processors have a simple RISC pipeline and the ability to augment the ISA with custom instructions. The ISA can be augmented statically, at tape-out, or it can be augmented dynamically when applications are loaded. The eMIPS processor is an example of a dynamically extensible processor.

Extensible processors take advantage of the fact that a small amount of code takes the majority of execution time in a typical program. The code that executes most often is a candidate for hardware acceleration. The code must be identified by a special instruction that will initiate the accelerator.

Selection of the best code to accelerate is an active area of research. The eMIPS tool-chain restricts the code selection problem to the set of basic blocks in the application. Using the strict definition in [1], the basic block is a directed acyclic graph (DAG). The BB-Tools select the basic blocks to accelerate and patch the binary image with the special instructions for the accelerator. The M2V compiler automatically generates the hardware accelerator.

The accelerator can be statically loaded when eMIPS is reset or it can be dynamically loaded when an application is loaded using partial reconfiguration of the FPGA. By dynamically loading and unloading accelerators, programmable hardware can be minimized.

In previous versions of eMIPS, the accelerator blocks could be specified and given to a hardware designer to hand design the accelerator. While this can lead to an efficient implementation, it does not scale well as dynamically extensible processors are more widely used. The use of tools like M2V can expand the use of hardware acceleration.

M2V accelerates applications from their compiled machine code. This is the only option when an application's source code is unavailable, such as when a third-party writes the application and keeps the sources. Accelerating from binaries can also be advantageous if multiple front-ends are used for development. A developer could use C, LISP, Perl, or any other high-level

programming language for their development, but they all must be compiled to machine code.

The remainder of this document is structured as follows. Section 2 discusses related work, Section 3 gives an overview of the eMIPS hardware platform, Section 4 goes through the M2V data structures and algorithms in detail. Section 5 explains how to run the M2V tool when a BBW source file has been generated. Section 6 goes through the source code implementation for M2V and Section 7 explains the hardware that is generated from M2V in more detail. Section 8 discusses the experimental results, Section 9 gives future research directions, and Section 10 concludes the report. Appendix I contains figures that illustrate scheduling for the primary example in the report. Appendix II contains the Verilog output from M2V for the example in the report. Appendix III contains the BBW file for the example basic block and Appendix IV lists the output from M2V when using the example basic block as input.

#### 2 Related Work

Work on extensible processors can be divided in several ways. One avenue of exploration is to define the underlying hardware. Chimaera [7] and GARP [8] are two examples of extensible hardware from the late 1990's. Commercial FPGA manufacturers today all provide examples of soft-cores, microprocessor designs that the customer can modify and extend for their application [15, 3, 13]. M2V uses the eMIPS processor [6] as its underlying hardware platform. eMIPS is the first design that is secure for general purpose multi-user loads, and the set of potential applications is therefore more open-ended than those found in the typical embedded system alone.

A common approach to generate code for an extensible processor is to modify an existing C compiler. Tensilica [14] regenerates a full GNU compilation system given the RTL of the new instruction. Ienne et al. [4] use the SUIF compiler. To the best of our knowledge, M2V is the first compiler that accepts as input binary machine code rather than source code. There are trade-offs between accelerating from source code in a high-level language or from binaries. One of the major advantages when accelerating from binaries is that any application can be accelerated, even applications where the source code is controlled by an outside party and not available to the system developer. A disadvantage is that some of the information that has been discarded must be reconstructed, and there are limits to this reversal process.

Another avenue of research in extensible processors is the identification of the instruction set extensions (ISE)

that most benefit a given program, see for instance [5] for a recent overview. Bonzini [5] advocates generating the ISE from within the compiler, Tensilica [14] from profiling data. M2V currently follows the application profiling approach; it uses the BB-Tools and dynamic full-system simulation with Giano to select the candidate basic blocks. A possible extension to our work is to use M2V in concert with a high-level compiler. Once the ISE is identified from within the compiler, its definition could be output in the form of a BBW file.

A related area is the generation of HDL code from C, the so-called C-to-gates design flows [11, 12]. The input to M2V is binary code, but the target is similar.

#### 3 eMIPS Hardware Overview

The extensible MIPS (eMIPS) processor [6] has been developed at Microsoft Research as an example of a RISC processor integrated with programmable logic. The programmable logic has many uses, such as: extensible on-line peripherals, zero overhead online verification of software, hardware acceleration of general-purpose applications, and in-process software debugging [2]. This report is concerned with automatically generating hardware accelerators.

The instruction set for the eMIPS processor is the instruction set for the R4000 MIPS processor [10]. The R4000 is an example of a classic RISC architecture. The eMIPS pipeline follows the classic RISC pipeline [9] consisting of five stages: instruction fetch (IF), instruction decode (ID), execute (EX), memory access (MA), and register write-back (WB).

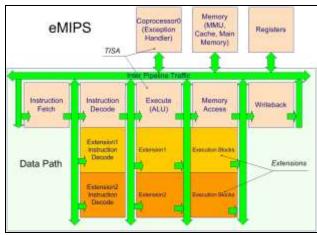

Figure 1: Block diagram of the eMIPS architecture.

The eMIPS processor departs from a standard RISC processor by adding an interface to programmable logic. The programmable logic is tightly integrated with the

RISC pipeline, it can synchronize with it and it can access the same resources as the RISC pipeline. Figure 1 shows a logical block diagram for the eMIPS processor, a physical view of the prototype is depicted in Figure A-8 and Figure A-9. The tight coupling of the pipeline and programmable logic creates a very low latency interface between the accelerator and the RISC pipeline.

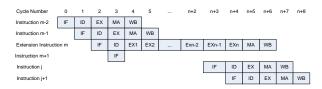

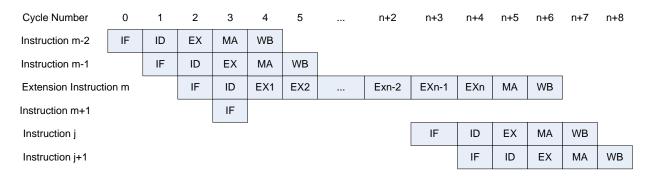

Figure 2 (and a repeated, larger, version in Figure A-1) illustrates the pipelining of instructions through eMIPS. The decode logic in the extension logic is always an observer of the main pipeline and is trying to decode the instruction in the instruction decode (ID) phase of the pipeline. When the instruction is not an extension instruction, the extension fails to decode it and it is executed in the main pipeline. When the instruction is successfully decoded by the extension logic, the extension logic is activated and the hardware accelerator is used. Instructions flowing through the main RISC pipeline prior to the extension instruction complete normally. Instructions following the extension are stalled until the extension is near completion, in the EXn-1 cycle.

Figure 2: Instruction flow through eMIPS pipeline.

The RISC pipeline imposes microarchitectural constraints on the extension logic, for instance in the arbitration for access to the register file and other resources. The extension logic needs to read and write the register file and access the memory management unit (MMU). These accesses by the extension logic are scheduled by M2V so as not to conflict with the primary RISC pipeline.

The primary RISC pipeline uses two read ports on the register file when an instruction is in the ID stage, it uses one MMU port when in the MA stage, and it uses one write port on the register file when in the WB stage. The eMIPS register file has four ports which are multiplexed between four read ports and two write ports. The extension logic has the potential to use all of the eMIPS register file ports, but it must not conflict with the primary RISC pipeline. Thus, register writes must be delayed by the extension until previous instructions are retired and register reads must be finished a couple of cycles before trailing instructions get to the ID stage.

As a specific example, when the extension instruction is in the EX1 cycle of execution, instruction m-1 is in the MA pipeline stage and so instruction m-1 has access to the MMU. Instruction m-2 is in the WB pipeline stage

and it has control of the register file write ports. The extension instruction does not have control of all the resources until stage EX3 when the previous instructions have been retired.

The eMIPS processor has been implemented on a Xilinx Virtex 4 FPGA using the ML401 evaluation board. The partial reconfiguration capabilities of this FPGA allow software to load dynamically the hardware for the instruction extensions.

# 4 The M2V Compiler

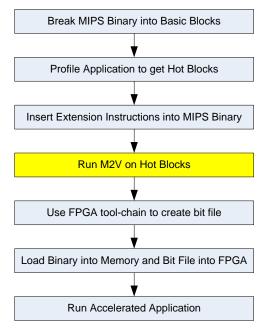

The M2V compiler is one element of a larger eMIPS tool-chain which is illustrated in Figure 3. The goal of the eMIPS tool-chain is to accelerate a pre-compiled application with the programmable extension logic in eMIPS. The goal of M2V is automatically generate the hardware which will be loaded into the extension unit.

Figure 3: Tool chain for accelerating basic blocks on the eMIPS architecture.

The eMIPS tool-chain includes the BB-Tools. The BB-Tools identify the basic blocks and then profile them on the Giano simulator to get dynamic execution counts. The basic blocks with the highest execution time (the hot blocks) are selected for acceleration. The BB-Tools generate an instruction encoding for the hot block and write out the BBW file (see section 4.1.1). The BB-Tools also insert the extension instruction into the original binary and patch any branch and jump addresses.

The M2V compiler takes the description of the hot blocks in the BBW file and automatically generates synthesizable Verilog for the extension. The Verilog for the extension can be synthesized with the standard FPGA synthesis tool-chain, which eventually produces a BIT file. The BIT file contains all of the programming information for the FPGA to implement the hardware of the extension. The BIT file can be statically loaded at reset of the FPGA or the operating system loader can dynamically load the BIT file using partial reconfiguration when the application is loaded into main memory.

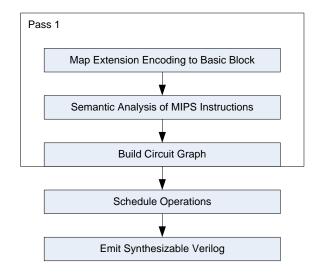

The M2V compiler makes three passes through the database as illustrated in Figure 4. The first pass processes the BBW file and consists of three major steps: map the encoding for the extension instruction to the basic block, analyze the MIPS instructions, and build a circuit graph. The second pass schedules the operations that are represented in the graph. The third pass emits the Verilog that will be synthesized and placed in the eMIPS FPGA.

Figure 4: Steps in M2V.

As the algorithm is discussed, it is helpful to use an example to reinforce the concepts. The example that was selected for this purpose comes from the analysis of video games and real-time applications [6]. This basic block implements part of a 64-bit divide on the 32-bit architecture of eMIPS. The assembly code for the example is shown in Figure 5, where the bracketed number is the hexadecimal byte offset for the instruction:

```

[ 0] ext0 r4, r2, offset0

[ 4] sll r1, r1, 1

[ 8] srl r3, r2, 31

[ c] or r1, r1, r3

[ 10] sll r2, r2, 1

```

[ 14 ] srl r3, r4, 31 [ 18 ] or r2, r2, r3 [ 1c ] sll r4, r4, 1 [ 20 ] srl r3, r5, 31 [ 24 ] or r4, r4, r3 [ 28 ] sltu r3, r1, r6 [ 2c ] beq r0, r3, offset0 [ 30 ] sll r5, r5, 1

Figure 5: Example basic block.

The instruction at address 0, *ext0*, is the extension instruction that is inserted by the BB-Tools and is not part of the original basic block. The shift-left-logical instruction at address 30 is in the branch delay slot and it will be executed within the basic block before the instruction at the branch target is executed.

# 4.1 Pass 1 – Process BBW File

The BBW file is the interface between the BB-Tools and the M2V compiler. The components in the BBW file relevant to M2V are as follows: extension instruction encoding, canonical register relationships, canonical value relationships, sequential MIPS instruction stream in the basic block, and the code size of the basic block. The first pass in the M2V compiler is to parse and analyze the BBW file. The BBW file for the example in Figure 5 is shown in Appendix III.

#### 4.1.1 Mapping Instruction Encoding to Basic Block

For the first revision of M2V, the extension instruction is encoded as a MIPS instruction of the "I" format. The instruction encoding is illustrated in Figure 6. In assembly, the "I" instruction is written:

Opcode\_name rt, rs, immediate.

| opcode | rs    | rt    | immediate |

|--------|-------|-------|-----------|

| 31:26  | 25:21 | 20:16 | 15:0      |

Figure 6: MIPS "I" instruction format used for the extension instruction.

The opcode that identifies the instruction must be unique or it will alias onto an existing instruction. The *rs* and *rt* fields are used to map two actual registers to two canonical registers. The *immediate* field is used for the branch relative address at the end of the basic block.

When the original MIPS executable binary file is broken into basic blocks, the registers are canonicalized. Thus the first actual register in the basic block is assigned

canonical register R1, the second actual register is assigned canonical register R2, etc. By using canonical registers, it is hoped that multiple basic blocks can be mapped to the same canonical basic block. This gives more opportunities to accelerate the application.

Basic blocks that are good candidates for acceleration will typically reference more than two registers. Since the instruction encoding only has enough bits to encode two unique registers, all other registers must be relative to these two registers. The relationships between *rs*, *rt*, and the other canonical registers are recorded in the BBW file and the relationships must be preserved in the hardware accelerator.

Likewise, there are only enough bits in the extension encoding to store one *immediate* value. If there are additional values in the basic block, they must be a constant for the basic block or the value must be relative to the encoded value. The BBW file and the hardware accelerator have the ability to use relative relationships between canonical values.

The relationships between the canonical registers and values are stored in a data structure that is later referenced when emitting Verilog. The data structure is used to generate the proper address for the register when the register file is accessed.

The code size for the basic block is not specifically part of the encoding, but the size is needed so that the program counter (PC) can be calculated for the fall-through case of the basic block.

#### 4.1.2 Analyze MIPS Instructions

The MIPS instructions must be analyzed to create the dependency graph, request pipeline resources, and emit the equivalent Verilog. There are three instruction formats in the MIPS I and MIPS II instruction set architectures supported by M2V: "I," "R," and "J".

The MIPS "I" format is illustrated in Figure 6. "I" instructions use a 16-bit immediate field as one of the operands. Examples of "I" instructions are ADDI, ANDI, BEQ, LW, SW, XORI, etc. Within the "I" instructions, ALU operations, branches, loads, and stores must be distinguished so that the correct dependencies can be built.

The MIPS "R" format is illustrated in Figure 7. "R" instructions read operands from registers and write results back to registers. Examples of "R" instructions are ADD, AND, SLL, etc. In assembly, the "R" instruction is written:

Opcode\_name rd, rs, rt.

| opcode | rs    | rt    | rd    | sa   | function |

|--------|-------|-------|-------|------|----------|

| 31:26  | 25:21 | 20:16 | 15:11 | 10:6 | 5:0      |

Figure 7: MIPS "R" instruction format.

The MIPS "J" format is illustrated in Figure 8. "J" instructions modify the program counter (PC) using the address field in the instruction encoding. Examples of "J" instructions are J and JAL. In assembly, the "J" instruction is written:

Opcode\_name address.

| opcode | address |

|--------|---------|

| 31:26  | 25:0    |

Figure 8: MIPS "J" instruction format.

Analysis of the instructions provides the register and constant operands, the function of the instruction, and the output register for the instruction. The cost of the function is also part of the analysis. The cost is an estimate of how much time the combinatorial logic in an instruction will take. The cost is used when scheduling to determine when paths in the hardware need to be pipelined.

# 4.1.3 Build the Circuit Graph

The circuit graph is the core data structure for the second and third passes of M2V. It is constructed using the analysis of the MIPS instructions to build dependencies between the instructions. The graph is built in a single pass, as each instruction is sequentially read from the BBW file. There are two types of nodes in the graph: register nodes and instruction nodes.

Instruction nodes represent a single MIPS instruction. Edges into the instruction node are the operands for the instruction. An edge out of the instruction node represents the result of the instruction being streamed to a register value.

Register nodes represent a value that has been read or calculated in the basic block. When the register node is a root of the circuit graph, it represents the basic block's initial read from the register file. To minimize contention on the register file, each register is read at most once from the register file and the value is stored locally in the accelerator. There can be up to 31 roots in the circuit graph representing each of the MIPS registers. An edge into the register node is a value coming from an instruction. An edge out of the register node represents the value being used as an operand to an instruction.

In hardware, the register node may be realized with a pipeline stage from one operation to the next, or it may be a bus without a latch. The scheduling pass determines whether the register node is pipelined or not.

# 4.1.3.1 The Register Table

The register table is an additional data structure that is not part of the circuit graph, but it is used to eliminate redundant register nodes and to determine which register nodes must be written back to the register file. The register table has an entry for each MIPS register. The table entry is initialized to be invalid. instruction uses a MIPS register, the register table entry for that MIPS register is read. If the entry is invalid then the value must be read from the register file and the entry will be updated with a pointer to the current register node. If the entry points to an existing register node, then an edge will be added from the register node to the instruction. When an instruction calculates a value and writes it to a register node, the register table entry for that MIPS register is updated with a pointer to the register node.

The register table therefore always contains the most current value for the MIPS registers. When all instructions have been processed by M2V, a final scan of the register table will indicate the register nodes that contain the basic block's final value for the MIPS registers. Each of these register nodes must be written back to the register file. A maximum of 31 writes, one for each MIPS register, will be sent to register file.

The circuit graph is the final collection of instruction nodes, register nodes, and edges between these nodes.

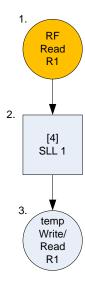

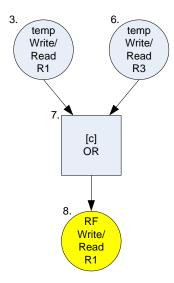

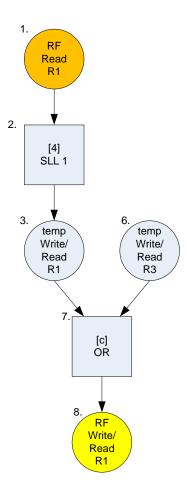

Figure 9: Graph for: sll r1, r1, 1.

# 4.1.3.2 Examples

The procedure for building the circuit graph will now be illustrated with some examples.

The instruction: [4] sll r1, r1, 1, is mapped to the graph illustrated in Figure 9. The constant shift value, 1, is an operand to the SLL instruction but it is not a vertex on the graph. Since M2V is producing custom hardware, a constant value can be easily optimized. The instruction uses MIPS register R1 both as an operand and as a result register. This creates two separate register nodes in the circuit graph. When the R1 operand is read, the register table entry is invalid so the register file must be accessed. The register table is updated to point to register node 1. When the result from instruction node 2 is written back, the register table entry is written with a pointer to register node 3.

The instruction: [ c ] or r1, r1, r3, is mapped to the graph illustrated in Figure 10. When the MIPS register R1 operand is read, the register table entry points to register node 3. This register node was generated from the sll instruction at address 4. The two instructions can share the register node. Since the register node is local to the hardware accelerator, the register file does not need to be accessed. Reducing the register file bottleneck is one area where the accelerator improves performance.

Figure 10: Graph for: or r1, r1, r3.

The circuit graph resulting from the two example instructions is illustrated in Figure 11. The sharing of register node 3 is more explicit in this figure.

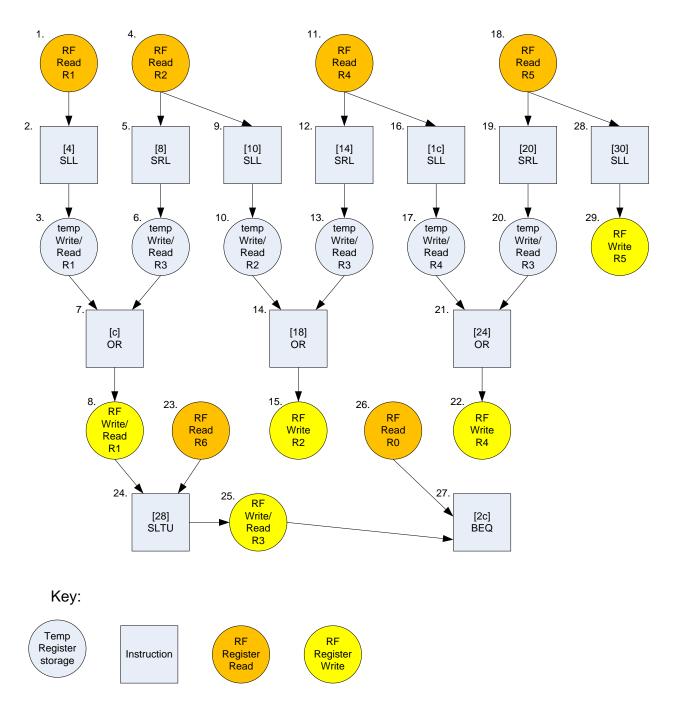

The circuit graph for the entire example basic block can be found in Figure A-2 in Appendix I.

Figure 11: Circuit graph for example instructions.

# 4.2 Pass 2 - Schedule Operations

After a circuit graph has been generated in pass 1 of M2V, the nodes in the graph can be scheduled. There are two major constraints that the scheduler must consider. First, the cycle time for the chip must be met and no combinatorial path can exceed the cycle budget. Second, the microarchitectural constraints of eMIPS must be respected. There are limited read and write ports on the register file and limited ports on the memory management unit. Also, the memory controller and the register file ports may not be accessible in every cycle due to the progress of instructions before and after the extension instruction through the RISC pipeline.

Figure 2 and Figure A-1 illustrate the progression of instructions through the eMIPS pipeline. In a regular unaccelerated instruction, the register file read port is accessible in the ID pipeline stage, the register file write

port is accessible in the WB pipeline stage, and the MMU is accessible in the MA pipeline stage. The extension logic respects these constraints and resources are blocked from within the accelerator when they would conflict with an instruction in the main RISC pipeline. A set of tables store the register file read ports, register file write ports, and MMU ports available to the extension logic on a cycle by cycle basis until steady-state is achieved. Steady-state is when the extension logic has control over all pipeline resources. Another set of tables store the resources that must be free at the end of the extension to prevent conflicts with trailing instructions.

There are four main data structures that are used in the scheduling pass of M2V: the register read list (RRL), the next temporary register queue (NQ), the temporary register queue (TRQ), and the register write queue (RWQ).

The register read list (RRL) was built as the circuit graph was created. The RRL contains all roots of the circuit graph and therefore represents all of the values that must be read from the register file.

The next temporary register queue (NQ) is empty at the beginning of each cycle. As the scheduling algorithm progresses, nodes are added to the NQ if the node has exceeded the cycle-time budget or if the node has unmet dependencies. The NQ represents all nodes that may need to be pipelined before the next cycle.

The temporary register queue (TRQ) is initially empty. At the beginning of each cycle, the NQ from the previous cycle is copied to the TRQ.

The register write queue (RWQ) is initially empty. A register value is placed on the RWQ when it has been calculated and it needs to be written back to the register file.

At the beginning of a clock cycle, the register file read ports, the register file write ports, and the MMU ports are calculated based on the values in the look up tables and the current cycle. The register read ports for this cycle dictate the number of nodes that can be removed from the RRL in this cycle. The register write ports for this cycle dictate the number of nodes that can be removed from the RWQ in this cycle. All nodes can be removed from the TRQ in a cycle because the nodes are temporary calculations that are local to the accelerator.

Nodes are scheduled by covering the circuit graph using a depth-first traversal from the nodes that are available from the TRQ, the RRL, and the RWQ. The traversal continues until a node is encountered with an unmet dependency or until the worst-case combinatorial delay from the last register exceeds the cycle budget. An unmet dependency is defined as an operand that has not

been read or calculated yet. A node is placed on the NQ when its traversal cannot continue.

The cycle ends when the TRQ is empty and the available nodes from the RRL and RWQ have been traversed as far as possible. The NQ is copied to the TRQ, the cycle is incremented, new resource constraints are calculated and the procedure repeats until the TRQ, the RRL, the RWQ, and the NQ are all empty.

Nodes on the TRQ may need to be pipelined or they may get covered later in the same cycle. Thus, when beginning the traversal of a node from the TRQ, the nodes should be examined to see if the original unmet dependency still exists. If the dependency exists the node will need to be pipelined, otherwise the node can be dropped.

The M2V scheduler is greedy: it allocates resources to the nodes at the heads of the RRL and the RWQ. A more optimal solution could potentially be found if different traversals were considered, although this could be more computationally expensive.

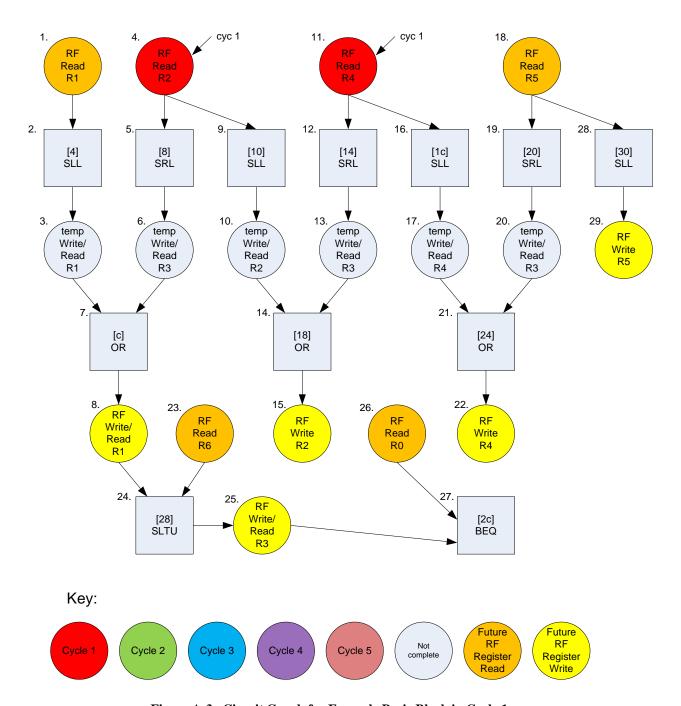

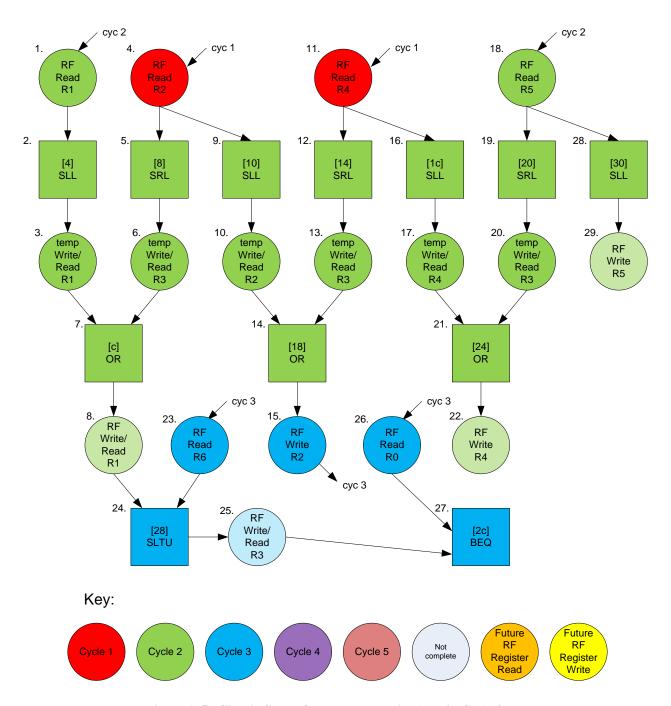

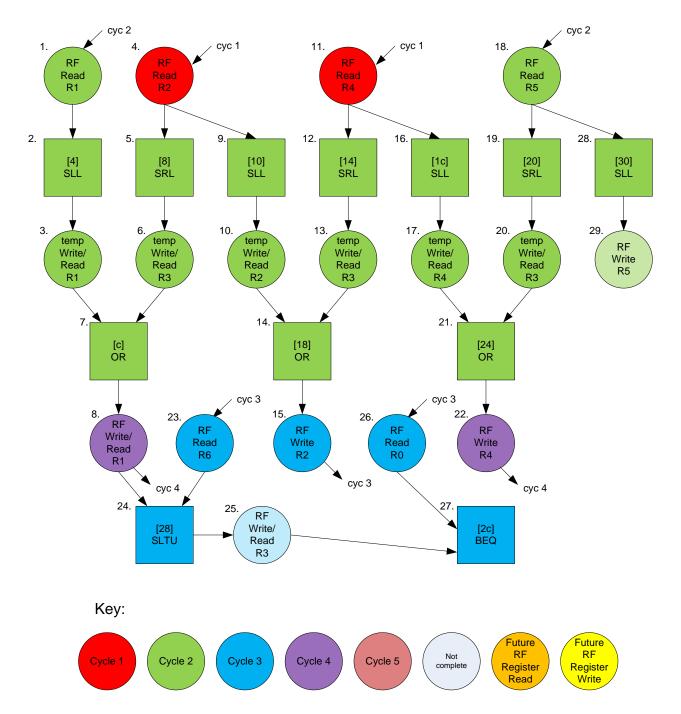

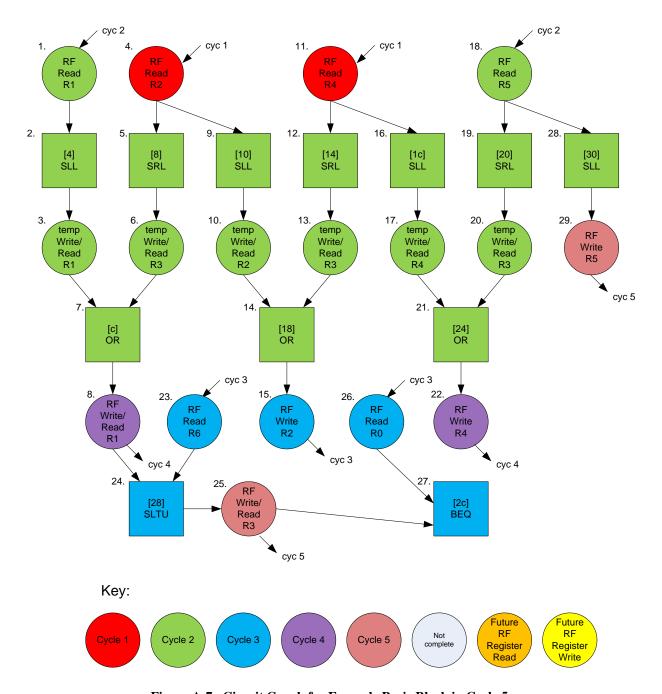

Appendix I contains a complete example showing how the basic block in Figure 5 is scheduled. Figure A-3 shows the circuit graph in cycle 1, the ID stage for the accelerator. Figure A-4 shows the circuit graph in cycle 2, the EX1 stage for the accelerator. Figure A-5 shows the circuit graph in cycle 3, the EX2 stage for the accelerator. Figure A-6 shows the circuit graph in cycle 4, the MA stage for the accelerator. Figure A-7 shows the circuit graph in cycle 5, the WB stage for the accelerator.

The unscheduled circuit graph is illustrated in Figure A-2. We will reference the nodes within the graph by their sequence numbers, which are located to the upper left of the node. At the beginning of the scheduling algorithm, all of the register read nodes (1, 4, 11, 18, 23, and 26) are on the RRL and the TRQ, NQ, and RWQ are empty.

Figure A-3 shows the circuit graph in cycle 1, the accelerator's ID stage. Register file reads during this cycle are limited to the two read ports accessed by the RISC pipeline since the accelerator is snooping the results from the RISC pipeline. The register read nodes 4 and 11 are covered in this cycle. Nodes 4 and 11 were removed from the RRL and placed on the NQ (the reads in the ID stage are placed on the NQ as a special case). The TRQ and RWQ are still empty.

Figure A-4 shows the circuit graph for cycle 2, the accelerator's EX1 stage. Two registers (nodes 1 and 18) were taken from the RRL and read from the register file, ten instructions (nodes 2, 5, 7, 9, 12, 14, 16, 19, 21, and 28) are calculated, and four MIPS register values (nodes 8, 15, 22, and 29) are calculated and placed on the RWQ. The NQ from cycle 1 was moved to the TRQ at the

beginning of cycle 2. The NQ at the end of cycle 2 contains nodes 6, 8, 10, and 17. Nodes 6, 10, and 17 were placed on the NQ speculatively because the operand nodes 3, 13, and 20 had not been read yet.

Figure A-5 shows the circuit graph for cycle 3, the accelerator's EX2 stage. The final read nodes (23, 26) are taken from the RRL and read from the register file, the final instructions (24, 27) are calculated, and register write node 25 is placed on the RWQ. The NQ from cycle 2 was copied to the TRQ at the beginning of cycle 3. The speculative nodes (6, 10, 17) on the TRQ are pruned when we notice that the successor instruction is already covered. Node 8 is removed from the TRQ, but it is placed on the NQ since the TRQ is emptied before any nodes on the RRL can be removed. The NQ also contains node 25 at the end of cycle 3. One register write (15) is removed from the RWQ and is written back to the register file. All nodes have been covered in cycles 1 through cycles 3, but the NQ and RWQ are not empty so the scheduling continues in the next cycle.

Figure A-6 shows the circuit graph for cycle 4, the accelerator's MA stage. The NQ from cycle 3 is copied to the TRQ at the beginning of cycle 4. Both nodes on the TRQ are pruned because the successor instruction node is covered. Two nodes (8, 22) are removed from the RWQ and written back to the register file. The RRL, TRQ, and NQ are empty. The RWQ has two nodes left and so the scheduling algorithm continues for another cycle.

Figure A-7 shows the circuit graph for cycle 5, the accelerator's WB stage. The final two nodes (25, 29) are removed from the RWQ and written back to the register file. All queues are empty and the scheduling phase is complete.

## 4.3 Pass 3 - Emit Verilog

The third and final pass in M2V is emitting Verilog. There are four contributions to the final Verilog file: the eMIPS invariant code, the BBW dependent code, the circuit graph dependent code, and the cycle dependent code.

The eMIPS invariant code, or boilerplate code, is the same for all eMIPS extensions. This Verilog code contains the interface to the primary eMIPS pipeline, routing through the bus-macros for partial reconfigurability, and the logic that is common for all extensions.

The BBW dependent code is Verilog that is specific to the instruction encoding and the register and value relationships encoded in the BBW file. During pass 1, the BBW information was extracted and stored in a data structure. The decode logic for the extension instruction

is generated using the opcode stored in the BBW file. The canonical register is sufficient as an identifier for temporary variables, but the actual register addresses must be used when accessing the register file. A table lookup maps between canonical register addresses and actual MIPS register addresses.

The circuit graph dependent code is generated with a final walk covering all the nodes in the circuit graph. As nodes on the circuit graph were generated and scheduled, the nodes were decorated with information that is now used to generate the final Verilog code. The circuit graph dependent code is: variable declarations for all register nodes, register file address and data logic, pipeline logic for register nodes that need it, and combinatorial logic for the instruction nodes.

The cycle dependent code is code that is generated for the state machines in the extension. This code is only dependent on the number of cycles in the extension and the general shape of the circuit graph is not important.

The Verilog code emitted for the entire example basic block in Figure 5 can be found in Appendix II. Additional description for the Verilog implementation can be found in Section 7.

# 5 Running the M2V Compiler

The makefile supplied with the BB-Tools will also compile the M2V tool. The command, "nmake", will compile all of the BB-Tools including m2v.exe using the visual C++ compiler. Alternatively, "nmake m2v.exe", will compile just m2v and its dependencies.

The command line for m2v is:

m2v.exe [-v] infile [outfile].

Typing m2v by itself will give the usage for the command. The optional verbose option, -v, sends information to standard out about how the compile is progressing. Details about the extension encoding, construction of the circuit graph, and scheduling information are output. The verbose option will also add comments to the combinatorial logic in the Verilog output so that a clear mapping between the MIPS binary and the Verilog can be seen.

The *infile* argument is the name of the BBW (.bbw) file that is used as input to the m2v compiler. The BBW file is generated by the BB-Tools. The optional *outfile* argument is the file name for the Verilog output. If an output file is not specified, the output is written to *a.v.*

The synthesizable Verilog generated by M2V can be simulated in the eMIPS infrastructure and it can be synthesized with the standard FPGA design tools.

Detailed instructions on how to synthesize an eMIPS Extension bit file are included in the eMIPS release documentation.

# **6** M2V Implementation Details

In this section we will discuss the structure of the M2V source code in more detail. The majority of the code for M2V was written in C++. The exception is the semantic analyzer, mips\_dissect.c, which was written in C. The main routine is in m2v.cpp. Other files of interest are: Circuit.cpp, Instruction.cpp, Register.cpp, and RegTable.cpp. Each of these files has a header file, \*.h, associated with it as well.

The *main* function in m2v calls the routines that step through each compilation pass. The first pass scans the BBW file which details the encoding of the extension instruction and enables the building of the circuit graph. The second pass schedules the operations using *Circuit.assignCycle* and the third pass emits the Verilog using *Circuit.emitVerilog*.

In pass 1, the parseEncoding procedure parses the extension instruction encoding from the BBW file. The encoding gives the extended op-code for the instruction, the canonical registers in the RS and RT fields, and the canonical value in the immediate field. There are not enough bits in the extension instruction to encode every canonical register in the basic block. To work around this problem, the basic block definition in the BBW file defines the fixed relationships between the registers that are actually encoded in the instruction and all the other canonical registers. For example, RS may hold canonical register R2, and canonical R1 could be defined as R1 = R2 + 1. The classes RegEncoding and ValEncoding (in m2v.h) store a single relationship and the BbwData class encapsulates all of the relationships which are needed when emitting Verilog in pass 3.

The semantic analyzer in pass 1 is implemented in the *MipsDissect* procedure. This procedure takes the binary encoding of a single MIPS instruction and produces the information needed to build the circuit graph and to emit the Verilog for this instruction in pass 3. To build the circuit graph we must determine the register operands and the destination register for the instruction. To emit the Verilog we need to record the function (semantic) of the instruction and the value of any immediate operands or constants. This information is stored in the *disRecord* structure (mips\_dissect.h), accessible via a pointer in the instruction node. This procedure creates one such structure for each instruction in the MIPS binary.

The *Circuit* class contains the data structures and procedures for building, manipulating, and using the circuit graph. The *dis2nodes* method completes pass 1 of the compilation. It uses the analysis from *MipsDissect* to build *Register* and *Instruction* nodes and connect them into a circuit graph. The *assignCycle* and *emitVerilog* methods are used for compiler passes 2 and 3.

The dis2nodes method uses the analysis information in disRecord to further divide a single MIPS instruction into an Instruction node and a few Register nodes, building (a fragment of) the circuit graph. Register nodes are needed for an instruction's operands and to store its result. When a Register node is created for the first read from the register file, dis2nodes pushes the node onto the register read queue, regRdVec, which is an entry point into the circuit graph. The edges of the circuit graph represent the dependencies between instructions and data and are stored within the Instruction and the Register nodes.

The *Register* class represents an intermediate value for a MIPS register. A value may come directly from the register file or it may be the result of an instruction. The value may need to be written back to the register file and it may be used as the operand to one or more instructions. The class maintains pointers to the source of the value and the destinations that use the value. The value in a *Register* node may be pipelined to make the cycle-time or it could be strictly combinatorial. A recursive walk method is used in pass 2 of the compilation to traverse the circuit graph when scheduling operations.

The *Instruction* class stores the results of the analysis in *MipsDissect* and maintains pointers to operand and destination data. A recursive walk method is used in the scheduling pass (pass 2) to traverse the circuit graph.

The RegisterTable class is a compile time resource that stores the current location of a MIPS register value. There is an entry in the table for each MIPS register. The entry is initially marked invalid. When an instruction within the basic block uses a MIPS register for the first time, a Register node is created and the RegisterTable entry for that register number is modified to point to the new node. Subsequent reads of the same register can then come from the Register node rather than from the register file. When an instruction writes to a register, a pointer to the instruction's result is stored in the RegisterTable entry. Maintaining the RegisterTable allows instructions to share Register nodes when the instructions use the same value and it minimizes accesses to the register file. The setWriteBacks method is called at the beginning of the second pass to determine which registers have been written during the basic block's execution. These Register nodes are marked and will be the only values written back to the register file.

Pass 2 of the compiler takes the circuit graph and generates a schedule for the operations. The top-level code for pass 2 is the *assignCycle* method in the *Circuit* class. The steps in pass 2 are to initialize the cycle-by-cycle resource restrictions, determine the MIPS registers that need to be written back, walk the entire circuit graph to assign cycles, and potentially add extra cycles to the extension to maintain proper pipeline behavior.

Access to the register file and to the memory controller is constrained because instructions in the eMIPS pipeline before or after the extension may own those resources. Three classes of variables define the resources available in each cycle. The *init\** arrays define the number of read ports, write ports, and load/store ports available in each cycle as the extension instruction starts. The *ss\** variables define the maximum number of resources available during steady-state execution. The *fin\** variables define the resources available as the extension is completing.

The array values used for register access are defined in the Circuit.h file. The Circuit.h file contains the architecture specific constants for eMIPS. By changing these constants, a different architecture could be supported. For revision 1.0 of M2V, there are 2 reads allowed in each cycle of the extension. There are 0 writes allowed in cycles 1 and 2, 1 write allowed in cycle 3, and 2 writes allowed in steady-state. Architectural explorations are possible by changing the constants in Circuit.h.

The walk of the circuit graph takes several iterations to complete, where each iteration represents a cycle in the hardware accelerator. During a cycle, all nodes will be removed from the TRQ, regTmpVec, some nodes will be removed from the RRL, regRdVec, and some nodes may be removed from the RWQ, regWrVec. The cycle number and the array values described above define how many nodes are removed from the RRL and RWQ.

The walk of the graph begins in a register node and continues depth first until an instruction with an unmet dependency is found or until the cycle budget is exceeded. The *walk* methods in the *Register* and *Instruction* classes perform the traversal through the dependents until there is an unmet dependency, the cost function is exceeded, or there is no successor to the node.

The cost is calculated by taking the cost from the previous node and adding the cost for this node. The maximum cost defined in Circuit.h is roughly the estimated logic levels from the last register. By keeping the logic levels within the cost function, the cycle budget should be met. For an instruction node, the cost is calculated by taking the highest cost from all of its operands and adding the incremental cost for the instruction. Since a register has a single entry point, the

cost is calculated by adding the incremental cost of the register node to the cost entering the node. The incremental cost is a function of fan-out since high fan-out will increase the wiring delay to subsequent nodes.

The walk ends when the return code from the dependent node indicates failure due to excessive cost or an unmet dependency. When the node receives a failure code from its dependent, the node is pushed to the NQ, *nxtQ*.

The register and instruction nodes are decorated with cycle, cost, and pipeline information during the walk. The sum of the decorations creates the final schedule and they are used to emit the correct Verilog in the final pass of the circuit graph.

When the allowed nodes have been removed from the TRQ, RRL, and RWQ in a given cycle, the next cycle can begin. Every cycle begins by copying the NQ from the previous cycle to the TRQ for this cycle. The scheduling pass is complete when the NQ, TRQ, RRL, and RWQ are empty.

The final pass of the circuit graph emits the Verilog for the hardware accelerator. The top-level method for this pass is *Circuit.emitVerilog*. This method combines invariant, BBW dependent, circuit graph dependent, and cycle dependent code in the correct order to produce the Verilog code for the hardware accelerator. The methods called by *emitVerilog* to produce the Verilog are described in Section 7.

The invariant part of the extension is stored in three Verilog files. The m2v\_mod\_bp.v file is the wrapper logic for the extension which contains the basic interface to the rest of eMIPS. The m2v\_ex\_bp.v file contains the module inputs and outputs between the extension logic wrapper and the logic for the execution stage in the extension. The m2v\_state\_mc.v file contains the declarations and logic for the read, write, and branch state machines that are the same for every extension.

# 7 Hardware Implementation Details

Appendix II lists the entire Verilog code that is generated by M2V for the basic block in Figure 5. As discussed in Section 4.3, there are four contributions to the final Verilog file: the eMIPS invariant code, the BBW dependent code, the circuit graph dependent code, and the cycle dependent code.

Lines 1-540 of the Verilog are the first lines of invariant code in the accelerator definition. Lines 1-300 define the extension's top-level module, lines 301-425 define the bus macros for the execution-to-write-back interface, and lines 426-540 define the bus macros for the

instruction-decode-to-execution interface. Lines 1-300 are simply copied from m2v mod bp.v at runtime.

The extension's top-level module defines the interface signals between the extension and the rest of the eMIPS design. It contains multiplexor logic for the shared data busses to the register file and the program counter update logic. It also instantiates four modules that make up the core of the extension: the instruction decode logic, the execution logic, and the two bus macro modules.

The bus macros provide connectivity between the extension logic and the primary eMIPS logic. They represent physical routing locations and are required for partial reconfiguration.

The instruction decode logic defined in lines 541-600 is BBW dependent code. This logic decodes the instruction in parallel with the primary RISC pipeline. If the opcode of the instruction matches the opcode of the extension, the logic will assert the RI signal so that the extension logic can take control from the RISC pipeline. The fall-through address for the basic block is sent to the program counter. The fields within the instruction are decoded and sent to the execution logic. The first revision of M2V hardcodes the extension instruction to the MIPS "I" format. The *Circuit.emit\_decode* method generates this code.

The extension execution logic is defined in lines 601-1038. The execution logic is composed of invariant code, BBW dependent code, circuit graph dependent code, and cycle dependent code.

Lines 601-666 define the interface signals between the execution logic and the rest of eMIPS. It is invariant for every extension and is copied from m2v\_ex\_bp.v at runtime.

Lines 667-695 define the Verilog registers that are used later in the execution logic. This code is circuit graph and cycle dependent. The registers for the register node values follow a convention to create an identifiable mapping between the generated logic and the circuit graph. The format is rX\_Y[\_r], where X is the actual MIPS register, Y is the sequence number of the register node, "\_r" indicates that the value comes directly from a register, and the absence of "\_r" indicates that the value comes from combinatorial logic. Thus, r9\_3 is a combinatorial value for MIPS register 9 that corresponds to the register node with sequence number 3. The *Circuit.emitVarDecl* method generates this code.

Lines 696-891 define the state machines that interface with the register file and the program counter logic. This code is invariant and is copied from m2v\_state\_mc.v at runtime. These state machines are eMIPS-specific.

Lines 892-924 define the register file and program counter usage for each cycle in the extension. This information is used by the state machines defined in lines 696-891. This code is generated by the *Circuit.emitCycState* method.

Lines 925-959 define the register file interface logic. Since there are limited ports on the register file, the read and write addresses are scheduled onto the register file address lines. Likewise, read data from the register file must be routed to the correct register node, and write data to the register file must come from the correct calculation. The *Circuit.emitRFLogic* method generates this code.

Lines 960-980 define the pipeline registers that are needed by the extension logic. When a calculation must be pipelined, it is latched at the end of the calculation cycle and held for the remainder of the extension's execution. The *Circuit.emitPipeReg* method generates this code.

Lines 981-1022 define the combinatorial logic for the instruction nodes. This code is generated by the *Circuit.emitInstLogic* method.

Lines 1023-1038 define the primary extension state machine. The state machine is 1-hot encoded with one state representing one cycle in the schedule so the states can be directly used as control signals. The machine is idle until an extension is successfully decoded and it steps through each cycle in the extension. The *Circuit.emitESM* method generates this code.

# 8 Experimental Results

The compiler is at its very early stages of development, but nonetheless the first simple test we ran gave very positive indications. We used the basic block of Figure 5, for which we already had both a hand-written version of the eMIPS Extension and a test program that exercised it. The test program executes some 500+ 64-bit division tests, validating the results against the tabulated ones. It is one of the standard basic validation tests for the Microsoft Invisible Computing RTOS.

|                | Hand-coded | M2V generated |

|----------------|------------|---------------|

| Minimum Period | 5.729 ns   | 5.886 ns      |

| Flip-Flops     | 755        | 494           |

| Slices         | 867        | 448           |

| 4-Input LUTs   | 1542       | 810           |

Table 1: Synthesis results.

The hand-coded accelerator and the M2V-generated accelerator were synthesized and verified on the Virtex-4 XC4LX25 FPGA, using Xilinx ISE v8.2i. The synthesis results are summarized in Table 1.

There are twelve instructions in the original basic block in Figure 5. With a CPI of 1, it takes twelve cycles to complete the unaccelerated basic block. M2V was able to accelerate the block such that it only needed five cycles resulting in a 2.4 speed-up, under idealized CPI conditions.

The actual speed-up of the application is dependent on the number of times that the basic block is executed over the course of the application and on the actual CPI. Notice that memory does not need to be fetched for instructions in the accelerated block, whereas it does for the unaccelerated one. On the ML401 board the SRAM chips have a worst-case latency of 3 cycles and a pipelined latency of 1 cycle, but only for batch-mode fetches (e.g. cache refill). Since eMIPS does not currently have a cache each instruction fetch costs 3 cycles. This gives a speed-up of 12 from reduced I-fetches alone, and a projected speed-up of 4.5 for the basic block in isolation.

The output and timing results from running the test program are shown in Appendix I, Figure A-14. Both versions obtained an overall speed-up of about 2.3 for the overall test program, over the unaccelerated version.

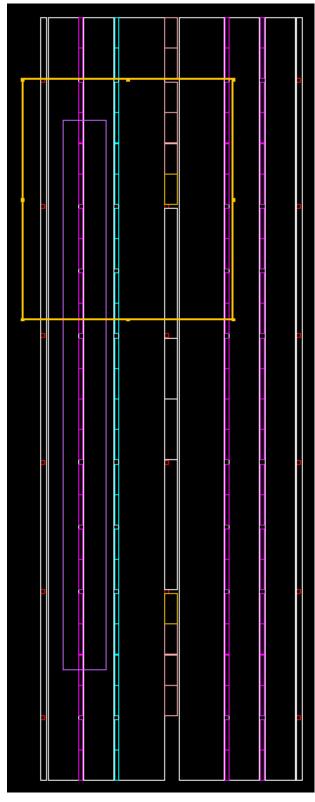

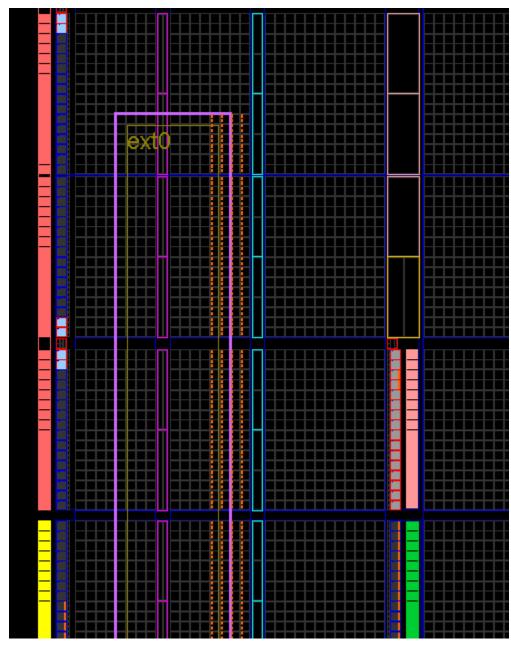

Of particular interest on eMIPS is the cost of an Extension in terms of its area utilization. The FPGA chip used on the ML401 board has fairly limited resources, being as it is the second-smallest chip in the Virtex-4 family of devices. The area we can devote to an Extension is consequently also limited. Figure A-8 is a rendition of the floor plan used for eMIPS, as depicted by the PlanAhead tool from Xilinx. On the left-hand side of the picture is the rectangle for the Extension logic. Figure A-9 shows a detail of the Extension floor plan, indicating the area used for the bus macros – the inter-connection points between the TISA and the Extension. There are many signals in the interface, and consequently a high-price to pay for them.

| Per-iteration speedup, CPI=1 (idealized) | 2.4  |

|------------------------------------------|------|

| Speedup from eliminated I-fetches        | 12.0 |

| Per-iteration speedup, CPI=3 (actual)    | 4.5  |

| Application speedup (actual)             | 2.3  |

| Area reduction factor                    | 2    |

| Maximum frequency reduction              | 2.8% |

Table 2: Summary of the performance results.

Figure A-10 shows a few selected statistics generated by the PlanAhead tool for the resource utilizations of the

hand-generated test extension. Of notice is the 58% utilization of the LUTs available in the Extension area. Figure A-11 shows the same statistics for the M2V-generated version, with a LUT utilization of only 30%.

The synthesis reports (before place and route) from the Xilinx ISE v8.2-PR are shown in Figure A-12 for the hand-generated version and Figure A-13 for the M2V-generated version, respectively. The reports confirm the PlanAhead indications of a factor of 2 area reduction. The timing reports show that the hand-generated version can potentially run at a higher frequency of about 175 MHz against 170 MHz for M2V. Both are well beyond the clock frequency of 100 MHz used on the ML401 board for eMIPS. Table 2 summarizes the various performance indicators discussed above.

#### 9 Limitations and Future Directions

The extension logic in eMIPS has direct access to the memory management unit (MMU), but M2V does not currently implement load and store instructions. Load and store operations can be both supported and optimized in the M2V compiler. Bandwidth to and from the memory can be increased by making the data path to memory wider than a conventional MIPS instruction would allow. For instance, an entire cache line could be read or written in a single cycle. Reads and writes can be reordered in the instruction stream to better hide latencies.

M2V must become aware of potential translation faults. The general scheme in eMIPS is to keep the original binary code in the executable, so that execution can be restarted from within it. M2V could keep a virtual program counter, associated with the register writebacks, to indicate where execution should restart in case of an MMU exception. This approach also solves the problem of handling external interrupts in a timely fashion.

M2V currently generates Verilog that executes in the minimum number of cycles for the given resource constraints. This can result in values being computed before they are needed. An additional pass through the graph could delay calculation of results until they are actually needed, a just in time approach. This would allow for idle hardware to be reused and could result in better overall utilization of the programmable logic.

Multiple basic blocks could be combined into a single accelerator. The state machines to control the control flow are simple, but multiple register tables might be needed to account for conditional branch instructions.

M2V is the first implementation of the general idea of taking a binary executable image and converting it to hardware. It understands MIPS instructions currently, but it could be extended so that the executable code could in fact be x86, ARM, or any other instruction set. Rather than targeting synthesizable Verilog, M2V could be modified to generate gates using a standard cell library or a number of other hardware elements. Note that if gates were to be generated directly, M2V would need additional optimization steps to improve the quality of the output. Currently, M2V takes advantage of the FPGA synthesis tools to perform a number of optimizations.

#### 10 Conclusions

By realizing M2V we have demonstrated that it is possible to automatically generate efficient hardware accelerators, starting directly from binary code. In contrast to existing approaches, M2V does not require any compiler modifications and therefore it supports any programming language and even cases where the code was directly written in assembly, or the sources are not available.

The implementation shows that the execution acceleration is based on a number of factors. Register file access is improved by scheduling register operations as soon and as efficiently as possible and by increasing the number of ports on the register file. Also, temporary writes and reads to the register file can be avoided as all intermediate results are kept in the accelerated logic.

Parallelism in the code is automatically extracted from the dependency graph. Instructions are built to proceed in parallel, as soon as their operands are ready. There are more operands available at any given time, because temporary variables are streamed directly to the instruction(s) that need them and there are more ports on the register file.

Multiple sequential instructions are executed in a single cycle when they fit within the cycle budget of the accelerator. For example, the SLL instruction can be executed in zero time on the hardware because it is only redefining the numbering of the bits within the bus.

The pressure on the memory bus and/or on the cache is greatly reduced. Memory bandwidth is freed up because the instructions in the accelerated basic block do not need to be fetched. In future revisions of M2V, loads and stores can be scheduled to optimize bandwidth resources and wider data-paths to the memory can also help.

# References

[1] Aho, A. V.., Lam, M. S., Sethi, R., Ullman, J. D. *Compilers: Principles, Techniques, and Tools*. Addison Wesley Publishers, Boston, MA. 2007.

- [ 2 ] Almeida, O., Forin, A., Garcia, P., Helander, J., Khantal, N., Lu, H., Meier, K., Mohan, S., Nielson, H., Pittman, R. N., Serg, R., Sukhwani, B., Veanes, M., Zorn, B., Berry, S., Boyce, C., Chaszar, D., Culrich, B., Kisin, M., Knezek, G., Linam-Church, W., Liu, S., Stewart, M., Toney, D. *Embedded Systems Research at DemoFest'07*. Microsoft Research Technical Report MSR-TR-2007-94, July 2007.

- [ 3 ] Altera Corp. *Excalibur Embedded Processor Solutions*, 2005.

.http://www.altera.com/products/devices/excalibur/excindex.html,

- [4] Biswas, P., Banerjee, S., Dutt, N., Ienne, P., Pozzi, L. Performance and Energy Benefits of Instruction Set Extensions in an FPGA Soft Core VLSID'06, pag. 651-656

- [ 5 ] Bonzini, P., Pozzi, L. Code Transformation Strategies for Extensible Embedded Processors CASES'06, pagg. 242-252.

- [ 6 ] Forin, A., Lynch, N., L., Pittman, R. N. eMIPS,A Dynamically Extensible Processor. Microsoft Research Technical Report MSR-TR-2006-143, October 2006.

- [7] Hauck, S. et al. *The Chimaera Reconfigurable Functional Unit*. IEEE VLSI, 2004.

- [8] Hauser, J. R., Wawrzynek, J. *Garp: A MIPS Processor with a Reconfigurable Coprocessor*. FCCM'97 pagg 12-21, April 1997.

- [ 9 ] Hennessy, J. L., Patterson, D.A. Computer Organization and Design: The Hardware/Software Interface. Morgan Kaufmann Publishers, San Francisco, CA. 1998.

- [ 10 ] Kane, G., Heinrich, J. *MIPS RISC Architecture*. Prentice Hall, Upper Saddle River, NJ. 1992.

- [ 11 ] Kastner, R., Kaplan, A., Ogrenci Memik, S. Bozorgzadeh, E. *Instruction generation for hybrid reconfigurable systems* TODAES vol. 7, no. 4, pagg. 605-632, October 2002.

- [ 12 ] Lau, D., Pritchard, O., Molson, P. Automated Generation of Hardware Accelerators with Direct Memory Access from ANSI/ISO Standard C Functions. FCCM'06, pagg. 45-54, April 2006.

- [ 13 ] Stretch, Inc. http://www.stretchinc.com 2006.

- [ 14 ] Tensilica, Inc. <a href="http://www.tensilica.com">http://www.tensilica.com</a>, 2006.

- [ 15 ] Xilinx Inc. Virtex 4 Family Overview. Xilinx Inc., June 2005. Available at http://direct.xilinx.com/bvdocs/publications/ds112.pdf

# Appendix I - Additional Figures

Figure A-1. Extension Instruction and interaction with MIPS Pipeline.

Figure A-2. Circuit Graph for Example Basic Block.

Figure A-3. Circuit Graph for Example Basic Block in Cycle 1.

Figure A-4. Circuit Graph for Example Basic Block in Cycle 2.

Figure A-5. Circuit Graph for Example Basic Block in Cycle 3.

Figure A-6. Circuit Graph for Example Basic Block in Cycle 4.

Figure A-7. Circuit Graph for Example Basic Block in Cycle 5.

Figure A-8. Floor-plan of the eMIPS processor. The area for the extension slot is the elongated purple vertical rectangle on the left side of the chip.

Figure A-9. Detailed view of the top portion of the Extension area. Bus macros are visible (orange dots) on the right side of the extension.

| Type of Site                                                                                                         | Available                              | Required                | % Utilization |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------|---------------|

| LUT                                                                                                                  | 2,760                                  | 1,614                   | 58.48         |

| FF                                                                                                                   | 2,760                                  | 755                     | 27.36         |

| SLICEL                                                                                                               | 690                                    | 492                     | 71.3          |

| SLICEM                                                                                                               | 690                                    | 492                     | 71.3          |

| FIFO16                                                                                                               | 16                                     | 0                       | 0             |

| RAMB16                                                                                                               | 16                                     |                         |               |

| Cellview Statistics                                                                                                  |                                        |                         |               |

|                                                                                                                      | Cou                                    |                         | U             |

| Cellview Statistics                                                                                                  | Cou                                    |                         | U             |

| Cellview Statistics Cellview Name                                                                                    | Cou                                    | ınt                     | U             |

| Cellview Statistics Cellview Name FD (hdi_primitives                                                                 | Cou<br>)<br>s)                         | int   567               | U             |

| Cellview Statistics Cellview Name FD (hdi_primitives FDE (hdi_primitive                                              | Cou<br>)<br>s)<br>ss)                  | int   567               | 0             |

| Cellview Statistics  Cellview Name  FD (hdi_primitives  FDE (hdi_primitive  FDR (hdi_primitive                       | Cou<br>s)<br>s)<br>es)                 | int   567   9   177     | U             |

| Cellview Statistics  Cellview Name  FD (hdi_primitives  FDE (hdi_primitive  FDR (hdi_primitive  FDRE (hdi_primitive) | Cou<br>s)<br>s)<br>ss)<br>res)<br>res) | int   567   9   177   2 | 0             |

Figure A-10. Statistics from PlanAhead for the hand-generated version of the mmldiv64 extension.

| Type of Site                                                                                              | Available       | Required             | % Utilization |

|-----------------------------------------------------------------------------------------------------------|-----------------|----------------------|---------------|

| LUT                                                                                                       | 2,760           | 817                  | 29.6          |

| FF                                                                                                        | 2,760           | 497                  | 18.01         |

| SLICEL                                                                                                    | 690             | 249                  | 36.09         |

| SLICEM                                                                                                    | 690             | 249                  | 36.09         |

| FIFO16                                                                                                    | 16              | 0                    | 0             |

| RAMB16                                                                                                    | 16              | 0                    | 0             |

| Cellview Statistics                                                                                       |                 |                      |               |

| Cellview Statistics  Cellview Name                                                                        | Cou             | ınt                  |               |

|                                                                                                           |                 | int 380              |               |

| Cellview Name                                                                                             |                 |                      |               |

| Cellview Name<br>FD (hdi_primitives)                                                                      | ;)              | 380                  |               |

| FD (hdi_primitives)<br>FDE (hdi_primitives                                                                | ;)              | 380<br>5             |               |

| Cellview Name<br>FD (hdi_primitives)<br>FDE (hdi_primitives<br>FDR (hdi_primitives                        | i)<br>i)<br>es) | 380<br>5<br>107      |               |

| Cellview Name<br>FD (hdi_primitives)<br>FDE (hdi_primitives<br>FDR (hdi_primitives<br>FDRE (hdi_primitive | s)<br>s)<br>es) | 380<br>5<br>107<br>1 |               |

Figure A-11. Statistics from PlanAhead for the M2V-generated version of the mmldiv64 extension.

Macro Statistics

# Registers : 755 Flip-Flops : 755

Device utilization summary: Selected Device : 4vlx25ff668-10

Number of Slices:

867 out of 10752

8%

Number of Slice Flip Flops:

755 out of 21504

3%

Number of 4 input LUTs:

1542 out of 21504

7%

Number of IOs: 324

Number of bonded IOBs: 0 out of 448 0%

Timing Summary: Speed Grade: -10

Minimum period: 5.729ns (Maximum Frequency: 174.557MHz)

Minimum input arrival time before clock: 3.270ns Maximum output required time after clock: 3.971ns Maximum combinational path delay: No path found

Figure A-12. Synthesis report for the hand-generated version of the mmldiv64 extension.

Macro Statistics

#Registers : 494 Flip-Flops : 494

Device utilization summary: Selected Device: 4vlx25ff668-10

Number of Slices:

448 out of 10752

4%

Number of Slice Flip Flops:

494 out of 21504

2%

Number of 4 input LUTs:

810 out of 21504

3%

Number of IOs: 324

Number of bonded IOBs: 0 out of 448 0%

Timing Summary: Speed Grade: -10

Minimum period: 5.886ns (Maximum Frequency: 169.894MHz)

Minimum input arrival time before clock: 5.029ns

Maximum output required time after clock: 6.351ns

Maximum combinational path delay: 5.494ns

Figure A-13. Synthesis report for the M2V-generated version of the mmldiv64 extension.

```

_ & ×

Visual Studio 2005 Command Prompt - serplexd -n -s

NOEXT TIME =

26£0033

BASELIME RESULTS

BASE START =

BASE FINISH =

BASE TIME =

0. 280506c

U. 511aefU

2915e84

EXTENSION TEST RESULTS

EXT START =

EXT FINISH =

EXT TIME =

0. 51bfd0a

0. 6402e4e

1243144

PERFORMANCE over base (base/ext) = PERFORMANCE over original (noext/ext) = OUERHEAD over original (base/noext) = TEST PASSED SUCCESSFULLY

> mmldiu64_ext.exe

HiMom! step= 42

GPI0 = 3

MARK - RUNNING NON EXTENSION TEST

READY...

SET...

GO!!!

DONE...

MARK - RUNNING BASELINE

READY...

SET...

GO!!!

DONE...

MARK - RUNNING EXTENSION TEST

READY...

SET...

GO!!!

DONE...

RESULTS

Errors -

NON EXTENSION TEST RESULTS

NOEXT START =

NOEXT FINISH =

NOEXT TIME = 20

0. 75697

0. 276b6са

26F0033

BASELIME RESULTS

BASE START =

BASE FINISH =

BASE TIME =

0. 280508d

0. 511af11

2915e84

EXTENSION TEST RESULTS

EXT START =

EXT FINISH =

EXT TIME =

0. 51bfd2b

0. 63886af

11c8984

PERFORMANCE over base (base/ext) = PERFORMANCE over original (noext/ext) = OUERHEAD over original (base/noext) = IESI PASSED SUCCESSFULLY

```

Figure A-14. Execution time results for the 64-bit division test program. The hand-generated version was run first, then the M2V-generated one

# Appendix II – Verilog Output for Example Basic Block

1

```

2

3

4

5

6

7

8

9

10

// auto-generated by m2v revision 1 on Wed Sep 19 14:47:36 2007

// INFO: reading from m2v_mod_bp.v

// m2v_mod_bp.v

// 8/15/07

// Karl Meier, Neil Pittman

12

13

14

15

// MIPS to Verilog (m2v) module (_mod) boilerplate (_bp)

// Copyright (c) Microsoft Corporation. All rights reserved.

16

`timescale 1ns / 1ps

18

19

module mmlite_div64 (

*********************

/****Ports**

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

/* INPUT PORTS */

CLK,

/* System Clock 50 - 100 MHZ */

input

input

EN,

/* Enable */

EXCEXT,

/* Exception Flush */

input

input

EXTNOP_MA,

/* Extension Bubble in Memory Access Phase */

/* Grant Pipeline Resources */

input

GR,

input [31:0]

INSTR,

/* Current Instruction */

input [31:0]

/* Current PC External */

PC,

input

PCLK,

/* Pipeline Clock */

/* Register Read Port 1 Register Data */

RDREG1DATA.

input [31:0]

input [31:0]

RDREG2DATA,

/* Register Read Port 2 Register Data */

input [31:0]

RDREG3DATA,

/* Register Read Port 3 Register Data */

input [31:0]

RDREG4DATA,

/* Register Read Port 4 Register Data */

/* Register Write Buffer Empty */

input

REGEMPTY,

/* Register Write Buffer Full */

input

REGFULL,

/* Register Write Buffer Ready */

input

REGRDY,

/* System Reset */

input

RESET.

/* OUTPUT PORTS */

/* Enable Acknowledged */

output

ACK.

output [31:0]

EXTADD,

/* Extension Address */

40

/* Multiplexed: */

41

42

43

44

45

Next PC */

Exception Address */

PC Memory Access Phase */

/* Conditional PC Update */

PCNEXT,

output

output [4:0]

RDREG1,

/* Register Read Port 1 Register Number */

46

/* Multiplexed: */

Read Port 1 Register Number */

48

Write Port 1 Register Number */

49

Write Register Memory Access Phase */

50

51

52

53

54

55

56

57

58

59

60

/* Read Port 2 Register Number */

RDREG2,

output [4:0]

/* Multiplexed: */

Register Read Port 2 Register Number */

Register Write Port 2 Register Number */

<0> Register Write Enable Memory Access Phase */

<1> Memory to Register Memory Acess Phase */

output [4:0]

RDREG3,

/* Register Read Port 3 Register Number */

/* Multiplexed: */

Register Read Port 3 Register Number */

RDREG4.

/* Register Read Port 4 Register Number Internal */

output [4:0]

/* Multiplexed: */

61

62

Register Read Port 4 Register Number */

/*

<1:0> Data Address [1:0] Memory Access Phase */

63

<2> Right/Left Unaligned Load/Store Memory Access Phase */

64

<3> Byte/Halfword Load/Store Memory Acess Phase */

65

output

REGWRITE1,

/* Register Write Port 1 Write Enable */

66

REGWRITE2,

/* Register Write Port 2 Write Enable */

output

67

output

REWB,

/* Re-enter at Writeback */

```

```

68

/* Reserved/Recognized Instruction */

output

69

70

71

72

73

74

75

76

77

78

80

81

WRDATA1,

output [31:0]

/* Register Write Port 1 Data Internal */

/* Multiplexed: */

Register Write Port 1 Data */

ALU Result Memory Access Phase */

WRDATA2

/* Register Write Port 2 Data Internal */

output [31:0]

/* Multiplexed: */

Register Write Port 2 Data */

Memory Data Out Memory Access Phase */

);

wire [31:0]ALURESULT_WB;

/* ALU Result to Writeback Phase */

82

83

84

85

/* Byte/Halfword Load/Store to Writeback Phase */

BHLS_WB;

wire

wire [31:0]CJMPADD;

/* Conditional Jump address to offset from Current PC */

wire [15:0]DIMM_EX;

/* Data Immediate Execute Phase */

wire [15:0]DIMM_ID;

/* Data Immediate Instruction Decode Phase */

86

DMADD_WB;

/* Least Significant Bits of Data Address to Writeback Phase */

wire [1:0]

87

wire [31:0]DMDATAOUT_WB;

/* Memory Data Out to Writeback Phase */

88

/* Execution Done */

wire

DNE:

89

/* Enable Execute Phase */

wire

EN EX:

90

wire [31:0]JMPADD;

/* Jump address to end of basic block */

MEMTOREG_WB;

/* Memory to Register to Writeback Phase */

wire

92

93

94

wire [31:0]PC_EX;

/* PC Execute Phase */

wire [31:0]PC_WB;

/* PC to Writeback Phase */

wire [4:0]

RD_EX;

/* Destination Register Execution Phase */

95

96

wire [4:0]

RDREG1_EX;

/* Register Read Port 1 Register Number Execute Phase */

wire [31:0]RDREG1DATA_EX;

/* Register Read Port 1 Register Data Execute Phase */

/* Register Read Port 2 Register Number Execute Phase */

wire [4:0]

RDREG2_EX;

98

wire [31:0]RDREG2DATA_EX;

/* Register Read Port 2 Register Data Execute Phase */

99

/* Register Read Port 3 Register Number Execute Phase */

wire [4:0]

RDREG3_EX;

100

RDREG4_EX;

/* Register Read Port 4 Register Number Execute Phase */

wire [4:0]

101

REGWRITE_EX;

/* Register Write Execute Phase */

wire

102

REGWRITE ID:

/* Register Write Instruction Decode Phase */

wire

103

REGWRITE_WB;

/* Register Write to Writeback Phase */

wire

104

RESET_EX;

/* Reset Execute Phase */

wire

105

wire [31:0]RESULT_EX;

/* Result Execution Phase */

106

RNL WB;

/* Right/Left Unaligned Load/Store to Writeback Phase */

wire

wire [4:0]

107

RS_EX;

/* Operand Register 1 Execute Phase */

108

wire [4:0]

RS_ID;

/* Operand Register 1 Instruction Decode Phase */

109

wire [4:0]

RT_EX;

/* Operand Register 2 Execute Phase */

wire [4:0]

110

RT_ID;

/* Operand Register 2 Instruction Decode Phase */

SLL128_EX;

/* Shift Left Logical 128 bits Execute Phase */

wire

112

SLL128_ID;

/* Shift Left Logical 128 bits Instruction Decode Phase */

wire

113

wire [31:0]WRDATA1_EX;

/* Register Write Port 1 Data Execute Phase */

114

wire [31:0]WRDATA2_EX;

/* Register Write Port 2 Data Execute Phase */

115

wire [4:0]

WRREG_WB;

/* Write Register Number to Writeback Phase */

116

wire [4:0]

WRREG1_EX;

/* Register Write Port 1 Register Number Execute Phase */

117

WRREG2_EX;

/* Register Write Port 2 Register Number Execute Phase */

wire [4:0]

118

119

120

121

122

123

/* Enable */

reg en_reg;