# **Embedded Systems Research at DemoFest'07**

Oscar Almeida, Alessandro Forin, Philip Garcia, Johannes Helander, Nishith Khantal, Hong Lu, Karl Meier, Sibin Mohan, Henrik Nielsen, Richard Neil Pittman, Risto Serg, Bharat Sukhwani, Margus Veanes, Ben Zorn

## Microsoft Research

Sarah Berry, Chris Boyce, David Chaszar, Brandon Culrich, Mikhail Kisin, Gabe Knezek, Warren Linam-Church, Steve Liu, Michael Stewart, Doug Toney

## Texas A&M University

July 2007

Technical Report MSR-TR-2007-94

Microsoft Research Microsoft Corporation One Microsoft Way Redmond, WA 98052

## **Embedded Systems Research at DemoFest'07**

Oscar Almeida, Alessandro Forin, Philip Garcia, Johannes Helander, Nishith Khantal, Hong Lu, Karl Meier, Sibin Mohan, Henrik Nielsen, Richard Neil Pittman, Risto Serg, Bharat Sukhwani, Margus Veanes, Ben Zorn

Microsoft Research

Sarah Berry, Chris Boyce, David Chaszar, Brandon Culrich, Mikhail Kisin, Gabe Knezek, Warren Linam-Church, Steve Liu, Michael Stewart, Doug Toney

Texas A&M University

#### Abstract

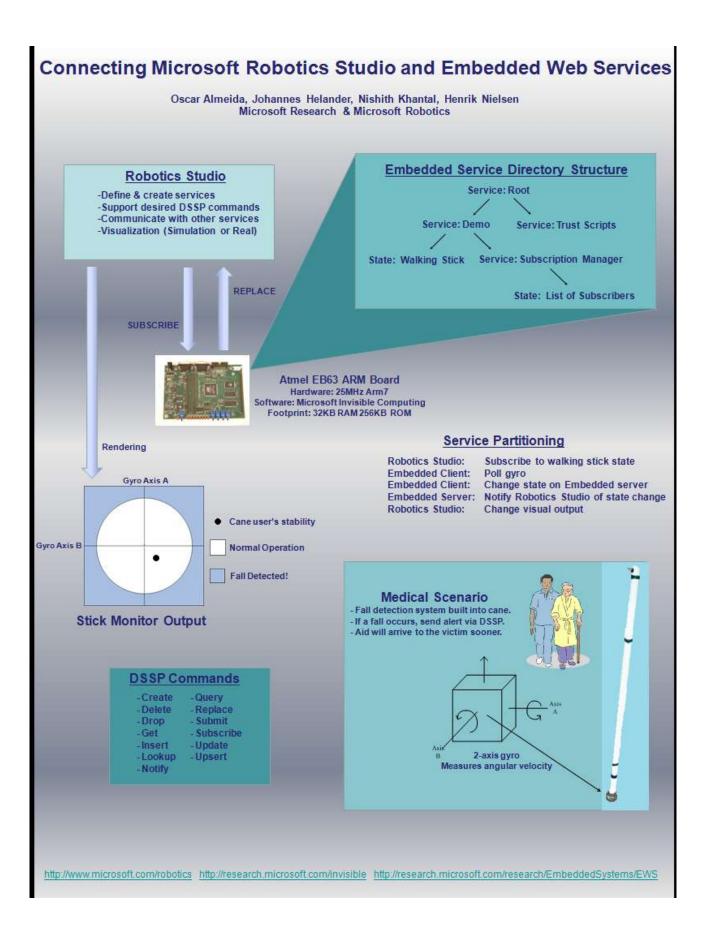

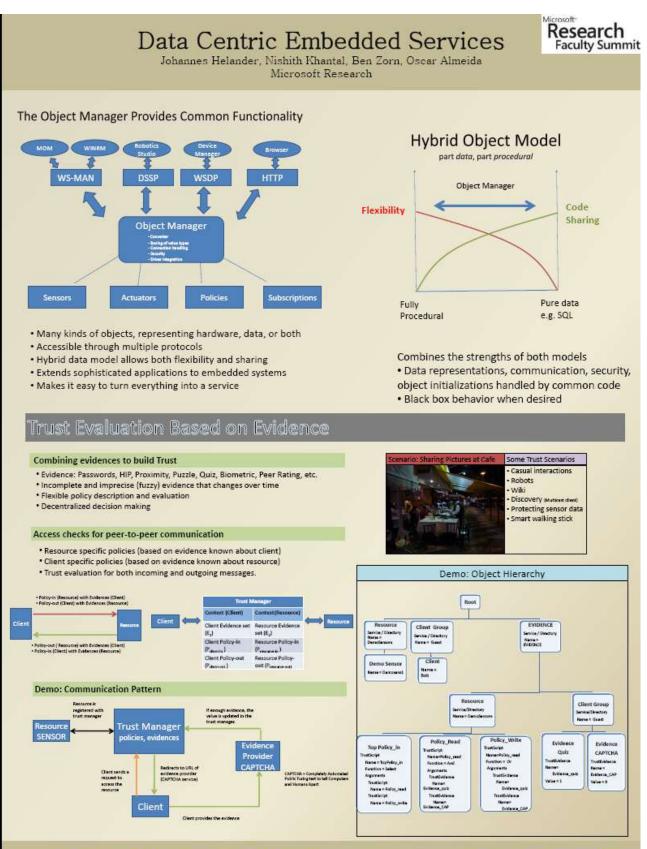

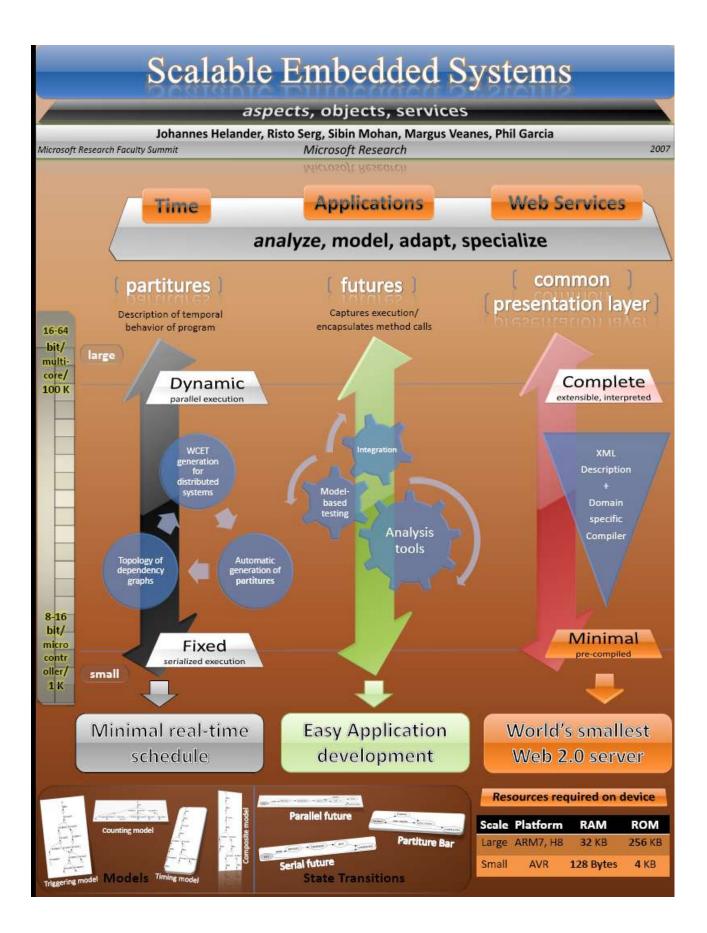

The Embedded Systems group at Microsoft Research has been engaged in joint academic collaborations spanning both teaching and research activities. The results of these collaborations are jointly reviewed, and highlighted to the academic community at the Faculty Summit at Microsoft headquarters in Redmond, WA, during the DemoFest event. This is also a good opportunity to review some of the other research projects that the group is engaged in, with special consideration to the research performed as part of the summer internships. This report presents the demonstrations that took place during the 2007 DemoFest. Two undergraduate student projects from the Real Time Distributed System group at Texas A&M illustrate the results of the teaching activities. The first was a six-motor robotic assembly capable of solving the Rubik Cube puzzle interactively, on an actual cube. The second was a 3D spherical display system realized with a rotating ring of LEDs controlled by twelve microcontroller boards, each board controlling a row of 18 multicolor LEDs. The research projects presented included the introduction of the first working prototype of the MSR eMIPS dynamically self-extensible microprocessor and three current intern projects that leverage the eMIPS architecture. Additional joint projects included a prototype of a data management system based on multiple trust evidence sources, illustrating a new approach to online and embedded security developed in collaboration with the Software Design and Implementation group. A walking stick for outpatient monitoring was the result of the collaboration between the Robotics and the Embedded Systems groups. Finally, scalability in Embedded Systems was the focus of two closely related projects. The first project realized the world's smallest Web2.0 server, using 2,636 bytes of code and 92 bytes of data on an 8-bit AVR microprocessor. This result leveraged the analysis and modeling tools realized in the second project, a collaboration with the Foundations of Software Engineering group that led to a hybrid static-dynamic tool for worst-case execution time estimation and off-line scheduling generation.

#### **1** Introduction

The Microsoft Faculty Summit is a workshop that has grown considerably over the years. This year, the attendance totaled nearly 350 highly qualified participants from universities across the globe. One of the most favorably received events at the Summit is the DemoFest event, when a large number of research projects and related activities are presented in a fair-like environment over a very short period of time (just about three hours!). This year the floor space, and consequently the number of booths, was somewhat reduced due to the widespread renovation work being carried out at the Microsoft Conference Center where the Summit takes place. The total number of booths was still high at 35, down only slightly from the 39 of the previous year.

The Embedded Systems Group has been present at the Summit since its inception, demonstrating both the results of its own research and the results of joint collaborations with academic partners and other researchers. This year we highlighted the ongoing collaboration with the Real Time Distributed Systems Group at Texas A&M University, with Microsoft Robotics, and with MSR researchers from the Software Design and Implementation Group and from the Foundations of Software Engineering Group.

The goal of this document is to attempt to communicate the vitality and excitement of the DemoFest event for those who could not attend it. While the atmosphere of free-flow communications and discussions is clearly impossible to reproduce, we can at least recapture and recount the artifacts and some of the practical demonstrations that took place in our small section of the event. Each of the document's sections is dedicated to one of the demonstrations that occurred at the event; it describes the demo in simple terms and reproduces and explains its outputs and screenshots. Each section has a corresponding poster that was displayed at the booth and which is reproduced in Appendix A. Short movies and memorable moments are recorded in Appendix B.

It is likewise impossible to describe the atmosphere of the days that immediately preceded the event, when the demos where finalized sometime very late into the night and very many and very busy people crammed into a couple of offices, interacting, arguing, feeding, competing, laughing, sleeping and generally helping each other reach a common goal of complete and amazing success. Our heartfelt thanks go especially to Sara Dangel and Claudia Boyle for their help with the ensuing bedlam, and to all our significant others for their patience and tolerance.

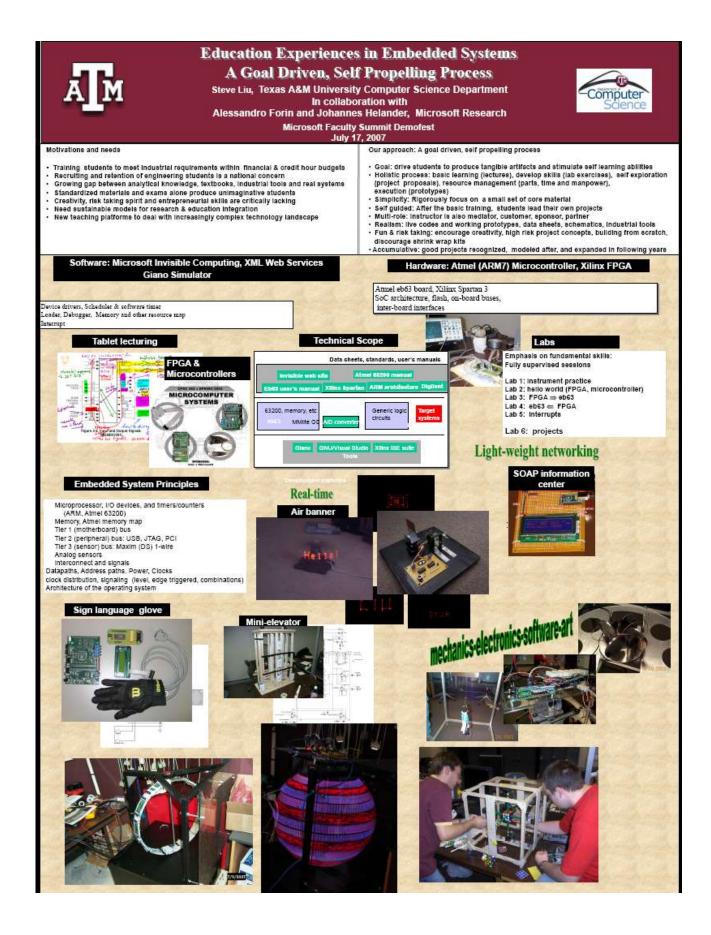

# Educational Experiences in Embedded Systems: A Goal Driven, Self-Propelling Process

## Steve Liu Texas A&M University

#### Abstract

Over the past five years, in partnership with MSR researchers, we have developed an experimental teaching strategy to explore more effective ways of teaching embedded computing systems to undergraduate students. Since its humble start, valuable experiences and tangible results continue to emerge. In this DemoFest we presented and shared the project's results. We found that disciplined creativity and explorative processes can steer students into a self-learning pathway that would be difficult to achieve by traditional lectures, tests and lab exercises alone.

In this strategy, the first half of the semester is driven by traditional lectures, exams and lab exercises aimed at imparting a baseline knowledge base. The second half of the semester is driven by open projects that require the students to deliver tangible prototypes, using the basic tools and materials learned in the first half of the semester. Specific learning objectives and methods are developed for different stages of the semester in order to achieve the stated technical goals of the class: "Exploration of students' creativity through group creation of entry-level, industrial grade toy projects using basic parts and tools."

#### 1 Introduction

A recent National Academy report, "Rising Above the Gathering Storm: Energizing and Employing America for a Brighter Economic Future (2007), " cites science and technology as critical assets to the security and prosperity of the United States. "Death by distance," a phrase used by the authors to describe the painful prospect of outsourcing professional jobs overseas, is a subtle yet real threat to the U.S. leadership in technology. While this issue needs to be addressed by the American society as a whole, higher education institutions face the immediate challenge of educating junior engineers who can serve the industry needs in the furiously competitive global market. This is particularly true for the information technology (IT) industry, which does not require heavy machinery investment to establish an operational base. The ongoing upheaval in the U.S. automotive industry is a clear hint of what will happen tomorrow if we do not act today on the pressing issues facing the American IT industry. Undergraduate education is responsible for producing the entry level engineers who perform the basic work. If domestic students cannot meet or surpass the productivity standards in the global market, the only alternative for a corporation to survive from global competition is to migrate the technical jobs to those places that can provide qualified workers at competitive wages. The last wave of outsourcing should be a clear reminder of this possibility. Unless we escalate both the number and professional preparedness of our engineering graduates, it will be only a matter of time before the U.S. loses its competitiveness in the global IT market.

Public universities are chartered with educating the larger student body with a broad background, within reasonable financial burdens for the students. Recruiting and retaining the undergraduate engineering students without compromising the curriculum's quality is a standing priority issue for many schools. Our experience is related to this issue, but some of the experiences provide greater insights on the effects of the new teaching approach. Our goal is to escalate the students' ability to transform technical knowledge into working systems at a minimal cost. Some self-imposed questions and our field experiences in addressing these questions in a large public university are highlighted in this report. Despite the progress made in the past several years (2002-present), our discoveries, experiences and approaches were limited to the Texas A&M campus. They may not necessarily be applicable to other institutions, and they should be interpreted with caution.

In this experiment, we took a clean slate approach in revising the course; literally everything related to the class—technical materials, labs, assignments, textbooks, technology, even the lab physical layout itself—are new. Our goal is to advance the technical competence of the students within existing credit-hour and prerequisite constraints. To achieve this goal, we based our experiment on the adjustment of the teaching-learning strategies, of the class objectives and of the technical materials. The entire process was supported by industry partners from Microsoft, Xilinx and ARM.

#### The Changes

Before our experiment started, the class was structured like most other classes in the curriculum but with the addition of a lab session. A textbook based on a popular microcontroller family was the only technical reference. The lab was based on a few exercises using the microcontroller covered in the book. Homework assignments, tests, and labs were the main tools for student learning and evaluation. The lecture materials were well structured and followed the book, and the lab was based on a few fixed exercises based on a separate lab manual. For students, this class setup represented a gradual transition from a learning process dominated by the textbook-exam scheme into an environment with some lightweight hands-on lab activity, and before they entered into their final senior capstone design class. Unfortunately, previous experience in teaching the senior capstone design course had shown that most students did not even know how to start a project, or were unable to transform their knowledge into a working system and therefore most students failed to bring the project to a successful completion.

We began by researching incremental changes to the existing technical materials and procedures in order to achieve our goals. This was eventually abandoned because of the following overriding concerns: (1) the textbook was very rich in content, but it was a major burden for both students and faculty. If a book is used as the main technical thrust there is little room left for other teaching options. (2) There was a significant gap between the lab materials and the textbook. (3) The existing process served the learning purpose well, but only for the heavily structured material in the book. Students would garner little experience in the discovery, usage and cross-reference of the broad and diverse technical data required to build practical working systems.

After an extensive search for textbooks, we found none that served our purposes effectively. We concluded that the only option left was to restructure the class from scratch. With the endorsement of both industrial collaborators and colleagues whose interests directly related to and were affected by the class, we decided to restructure it using a total hands-on approach to teaching and learning. We replaced the textbook with real microelectronic chip datasheets and schematics, supplemented by lectures on basic system design. Instead of developing monolithic but trivial applications on the microcontroller board, we choose to run a small open source, componentized, real time operating system (*Microsoft Invisible Computing, aka MMLite*). We consider the addition of the real time operating system to the microcontroller an important decision because, for instance, most modern handheld devices require some operating system functions. Students would learn to create embedded software that can coexist with and leverage other pre-existing software modules. We added an FPGA board to the hardware contents because of its widespread use in modern microelectronics systems. We chose not to use testing as the primary tool to assess the students' performance in class; instead, we gave more weight to the lab sessions and, most importantly, to the final open project. This reflected our view that basic knowledge can be checked by written tests, but system design skills and creativity can only be tested by labs and projects.

#### **Faculty and Student Roles**

A class is a human-centric system where faculty, students and teaching materials are the inputs, and the new knowledge and experience acquired by the students are the outputs. The traditional wisdom is to deliver the material in the most structured way possible in order to maximize the amount of knowledge that the students will gain from the class. The structure of the body of knowledge, the communication between faculty and students, the assignments, the tests, and the labs form the crux of most classes. For many fields in science, mathematics, engineering and technology (SMET), interaction mechanisms that are student-oriented and multidimensional can serve the learning objectives effectively. But whether the same can be said about education in information technology needs to be examined carefully.

In our approach, the semester is informally divided into two parts. In the first half the instructor and teaching assistants deliver the basic system concepts, lab procedures and examples to bring the students to the minimal technical level sufficient to perform basic development functions. The second part of the semester is instead driven by the students to bring their open project to completion. The faculty plays many roles in this second half of the semester:

- Consultant for project ideas and strategies;

- Mediator for dispute arbitration;

- **Sponsor** to finance the projects' purchases;

#### - **Judge** for the final evaluation.

Students begin the semester as passive learners, but soon they must explore their design options and the available parts needed to complete their project. The second half of the semester essentially becomes a self-propelled, self-learning process.

#### Hands-on and Fun

Fun and curiosity are the key factors that stimulate the students' willingness to tackle advanced ideas and transform them into working systems. The value of building an artifact is lost on the students when it cannot be shown to friends, or if they do not find it interesting. This is a particularly important issue for embedded computing systems, because of the tight integration of hardware, software, algorithms and even mechanical design into any complete, working system. Granted, learning to construct computing systems is important in its own right, and the integration of the computing devices with their environment, e.g., power, sizes, mechanical structures, etc., is also a major challenge. But rather than attempt to instill the proper design rules in advance, experience has taught us that leaving all options open to the students leads to a more effective self-learning experience. Our approach is to use a challenge-response process while mentoring the students in the pursuit of their technical goals. Students are challenged at every stage about the scope and progress of their projects, but there is no definite correlation between their adoption of the instructors' inputs and the final project outcomes. In fact, some of the best projects were realized in total defiance of the instructors' suggestions. Nonetheless, when the challenge-response process is used in conjunction with the instructor's sponsorship incentives, it clearly stimulates the students to think out of the box and to take on more interesting projects.

Students can use any information and any available design reference, provided that they can properly justify the value-added to their own project. They are allowed to regroup, and to scale up or scale down as their projects progresses with time. They can even redirect the project goals if appropriate. Freedom however comes with responsibility; students are held responsible for the way they use the information, for how they manage the intra-team relationships, and for the ultimate outcome of their project. Projects are graded based on the value that is added during the process. This value added could be quantified in terms of creativity, engineering process, or even the (failed) attempt to take on exceedingly difficult problems. Safe or "canned" projects receive the lowest and possibly failing grades.

From the teacher's perspective, the objective of hands-on and fun is not the artifact itself, but rather the stimulation of the students' creativity, knowledge usage and teamwork. The result of the final project is only a portion of the final grade; even a failed project can receive a good grade if the team can demonstrate high quality in their project development process. The level of challenges, creativity, and teamwork vs. accountability are all important decision factors. Students are encouraged to follow and to expand upon the successful projects from previous semesters. Admittedly, some projects did resemble each other but every semester has produced at least one very interesting project that is worth preserving and that will be cited as example in the next semester. Outstanding projects are submitted to the DemoFest fair to share our experiences with participating faculty. The history of exceptional projects is maintained in a website, and together with the exposure at DemoFest it creates further motivation for the new students.

#### Literature vs. Textbooks

A critical decision made at the beginning of this project was to eliminate the textbook in favor of real microelectronic datasheets, source codes and some basic system design lectures. We did not make this choice lightly. For generations the textbook has been the proven tool to pass knowledge from one generation to the next. It will continue to play this critical role in our teaching system, but it is not the only tool that can be used for a design-oriented, embedded computing class. Rarely do two embedded computing systems look alike; for decades in this field, very few convergent theories, architectures, or computing models have been agreed upon. New technologies constantly emerge from industry and many of them have very short life spans. Although datasheets are not written in the clear format and style of textbooks, most are written in fairly simple language and with complete technical information. We have classified the datasheets in two types: architectural and functional pages, and reference pages. Reference pages are not covered in the exams but functional pages are. While it may appear less convenient to students, there is a compelling reason to expose them to the original technical documents as they learn real system design.

Some websites are easy to navigate, while others are very difficult. Similarly, some datasheets are much easier to read than others; it may take weeks for a full-time engineer to go through some particularly voluminous and detailed set of datasheets. Unless they have some prior internship experience in the industry, most students assume that the textbook is their only source of knowledge. Luckily, technical information for undergraduate-level students is abundantly available from many different sources. Very few students, however, are able to navigate through the many sources of information

and their required tool chains and then transform them into working systems. Helping students make the breakthrough and move from the class to industry is very difficult if we maintain the teaching and learning processes of the past.

The other major concern with a textbook is the timely delivery of contemporary and updated knowledge to the students, because it can take months or even years before a good textbook can be written about a new subject. Requiring students to use industry datasheets in the class can be quite intimidating, but we might not be able to find a textbook that balances the well structured abstraction against the detailed and complete information. Therefore, we have no alternative but to make selective use of some well written datasheets to better serve the purpose of bringing the students closer to the real world of system design and development. "Time to market" is an industry expression that captures the tension to deliver a product to the consumer in the shortest time possible, to avoid rapid obsolescence and loss of consumer interest. Similarly, we might define as "time to classroom" our own struggle in the education field to bring to the student materials that are current and therefore improve on the market value of the knowledge that the students acquire.

#### **Industry Collaboration**

A primary objective of this experiment is to find the teaching methods that most elevate the students' professional preparedness. Experience tells us that there is a strong correlation between the degree of interaction between industry and university and these educational outcomes. This interaction must lead to face-to-face dialogues that can be translated into classroom-business actions. Ever since the inception of our collaboration, our MSR partners have played a critical role in the progress that we have been able to make. The first natural question was how to better match students' skills and industry expectations. It turns out that this issue does not have a standard answer, and, rightfully, should not. Industrial needs change with time, and the delivering of contemporary technological knowledge to the classroom is only one small part in the effort to make a quantum leap in educational outcomes. Material engagement in the classroom activities and genuine interests from industry are critical to keep the class lively and interesting for both faculty and students. Our joint projects in the DemoFest have proven highly effective in keeping the collaboration energy focused and vibrant.

In summary, we believe we have identified a sustainable, productive educational model that can enable other faculty with similar interests to reenergize their classes. It is not easy to get this far, particularly considering the existing fiscal and curricula restrictions and the students' resistance to change, but the outcomes speak for themselves. Students are able to complete far more advanced projects in their capstone design courses, and they demonstrate greater confidence in their job interviews. And the project results get stronger and stronger with the years. This year is another good year, and we look forward to an even better future.

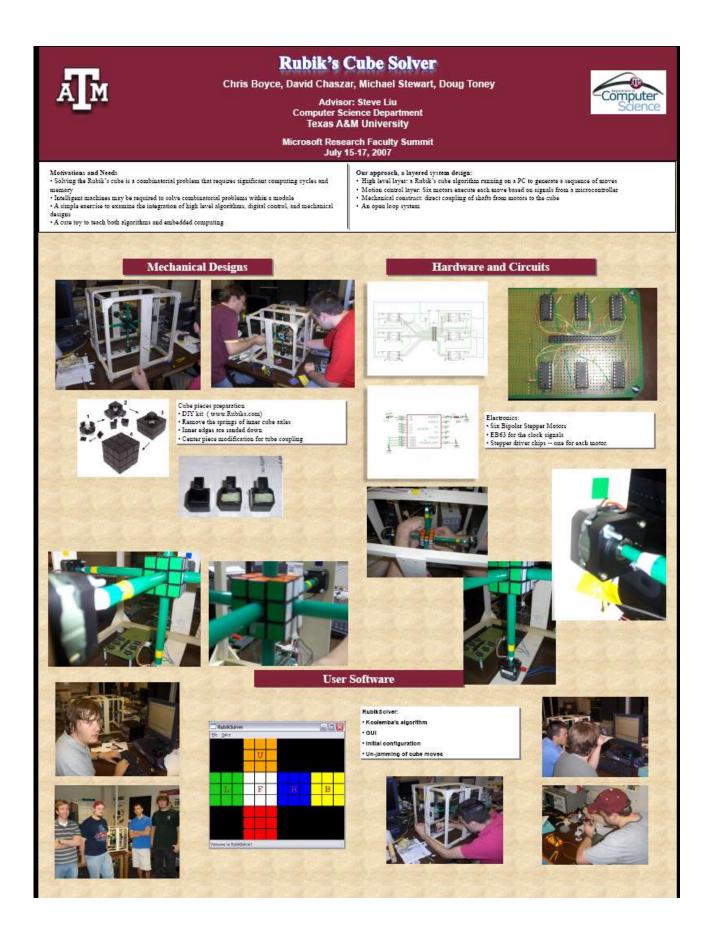

## **Rubik's Cube Solver**

## Chris Boyce, David Chaszar, Michael Stewart, Doug Toney, Steve Liu Texas A&M University

#### Abstract

The Rubik's cube solver is a multilayer embedded computing-motion control system that is capable of moving a Rubik's cube from an arbitrary initial state to the solved state. The high level cube solver is based on the Kociemba's algorithm and was implemented by Michael Reid (source: <u>http://www.cubeman.org/</u>). An EB63 microcontroller evaluation board running an application built with Microsoft Invisible Computing receives the motion commands from the high-level solver running on a PC, and moves the cube accordingly by rotating one of the faces at a time. We built a hardwood frame, mounted six stepper motors on the frame and directly coupled them to the cube to make the moves. Each axel links one stepper motor to the center element of one of the cube's faces. The whole project was completed within a few weeks from the assignment and demonstrates the students' abilities to transform their knowledge into a working system. Except for the RubikSolver software, all other software and hardware circuits and their controlling functions were realized by the students with minimal assistance from the instructor.

#### 1 Introduction

RubikSolver is the GUI/solving portion of the Rubik's cube solver. It is solved separately on the PC because the algorithm used [1] (Kociemba's algorithm) is fairly space and CPU intensive, more than the EB63 can perform within a reasonable time frame. It uses the COM2 port on the PC in order to send the motor commands to the EB63, but it is also possible to just solve the puzzle without sending the solution to the motors.

Kociemba's algorithm is implemented as a non-optimal solver first formalized by Herbert Kociemba. The solving algorithm we used is modified from source code provided by Michael Reid. The code was originally acquired from <u>http://www.cubeman.org/</u>, where Reid's Near-Optimal Cube Executable and Source is provided freely to the public. We have made many changes to the original version. We have ported the source code to C++, and moved all of the algorithm code into its own class (*KociembaAlgorithm*) under its own namespace (*Kociemba*). Additionally, several of the structs have been changed into classes and their members made private (*Cube, Options*), as well as using C++ friend declarations to ensure smooth transition (*Options*). *Cube* has been moved into its own namespace (*Rubik*) along with several constants that might be useful for future algorithm implementations. *KociembaAlgorithm* derives from a base *Algorithm* class which also helps make it easier to implement other algorithms in the future. The end result is that we have reduced pollution of the global namespace with algorithm specific constants and classes. Additionally, many of the #define'd constants have been made either static const or made into enums to help enforce type safety. Finally, the original printf and scanf routines have been replaced with much safer C++ streams, which makes input and output to the algorithm much more flexible.

## 2 Demonstration

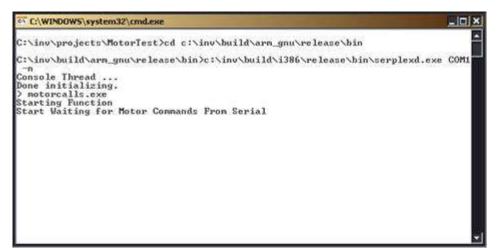

We start the demonstration by running RubikGUI.exe on the PC side and motorcalls.exe on the EB63 side. When motorcalls is initialized and ready for operation the console screen output from the board is as shown in the following screen. This indicates that the controller is waiting for the string of commands, which are expected on the second serial line connector of the EB63 board.

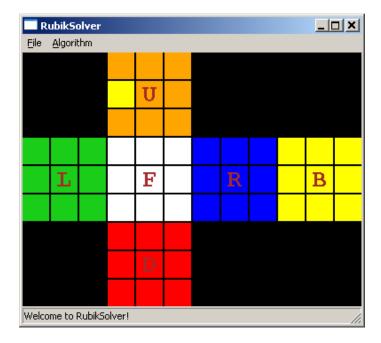

Once the GUI screen appears, there are several options. We can load a preset cube puzzle, create and save a new one, or enter the current state of the actual cube. The color of a square is selected by rotating through the six available color options, a left-click cycles in one direction and right-click in the other. Cubes must be entered from left to right, top to bottom facing the side. The following picture shows the GUI offered to the user. Faces are marked individually to help locating the corresponding ones on the actual cube.

Once the cube puzzle has been entered in the GUI, we can select **Algorithm->Solve** or **Algorithm->Unsolve** and the program will pop up a window saying whether or not the current entered cube state is valid.

After confirming that the cube state is correct, the GUI creates a new window titled 'Algorithm Setup'.

| Algorithm Setup        | <u>×</u> | ( |

|------------------------|----------|---|

| Metric:                | ▼        |   |

| Max number of solution | ons: 1   |   |

| Limit Stage 2 depth:   | 0        |   |

| Solve                  | Cancel   |   |

Here the user is presented with three options: the metric to solve for, the maximum number of solutions, and the depth limit of the Stage 2 solver. The metric determines what the solver tries to minimize, either face turns or quarter turns (face turn is faster). Since there is potentially more than one possible solution to a puzzle, the user can select the maximum number of solutions to collect before exiting (suggested 1, 0 for no limit). The depth parameter controls the search space expansion strategy; we recommend keeping it at 0 (indicating no limit).

Once the options are set we click Solve, and a solution window appears with the moves required:

| Solved Output      | × |

|--------------------|---|

| Algorithm output:  |   |

| corner-eflip space |   |

| 01                 |   |

| 14                 |   |

| 2 46               |   |

| 3 504              |   |

| 4 5662             |   |

| 5 61008            |   |

| 6 549711           |   |

| 7 2422226          | • |

|                    | × |

| Send Motor String  |   |

| Close              |   |

To actually move the real cube we click **Send Motor String**, and the string of commands is sent to the EB63 over the serial line COM2. The final result of the motion commands is as follows:

- If we fist clicked **Algorithm**->**Solve**, the motor string will solve a scrambled cube to a clean cube.

- If we fist clicked **Algorithm**->**Unsolve**, the motor string will solve a clean cube to a scrambled cube.

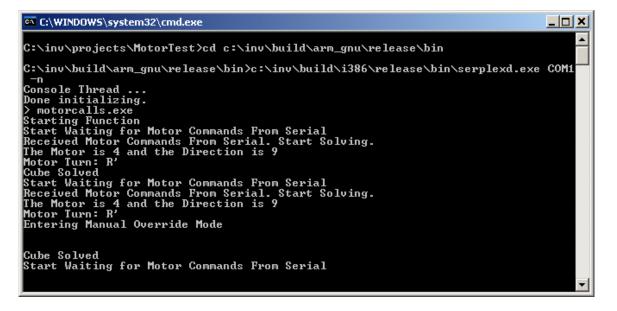

Now the move instructions go to the EB63. The EB63 will echo in the console (visible on the DOS window below) each command it receives:

| C:\WINDOWS\system32\cmd.exe                                                                  | _ [] | × |

|----------------------------------------------------------------------------------------------|------|---|

| C:\inv\projects\MotorTest>cd c:\inv\build\arm_gnu\release\bin                                |      | - |

| C:\inv\build\arm_gnu\release\bin>c:\inv\build\i386\release\bin\serplexd.exe<br>-n            | COM1 |   |

| Console Thread                                                                               |      |   |

| Done initializing.                                                                           |      |   |

| Starting Function                                                                            |      |   |

| Start Waiting for Motor Commands From Serial                                                 |      |   |

| Received Motor Commands From Serial. Start Solving.<br>The Motor is 4 and the Direction is 9 |      |   |

| Motor Turn: R'                                                                               |      |   |

| Cube Solved                                                                                  |      |   |

| Start Waiting for Motor Commands From Serial                                                 |      |   |

|                                                                                              |      |   |

|                                                                                              |      |   |

|                                                                                              |      |   |

|                                                                                              |      |   |

|                                                                                              |      |   |

|                                                                                              |      |   |

|                                                                                              |      | - |

As shown above, in this case the program received a single command to move the **Right Motor** Counterclockwise 90 degrees. The encoding for "Motor Turn" is:

#### R = 90 degrees Clockwise R' = 90 degrees Counterclockwise R2 = 180 degrees Clockwise

And similarly for the other motors, marked as in the GUI with the letters U, L, F, R, B, and D. The program will indicate **Cube Solved** when it has reached the end of the solve string.

#### **3** Lockup Resolution

It is possible for the cube to either lock up due to excessive friction, or to perform a partial rotation due to insufficient friction. In case the cube malfunctions and is locked in an invalid configuration it is possible to manually operate the motors and to continue solving. The **Manual Override** feature allows the user to move the sides of the cube manually. Three buttons on the board are used to implement this feature:

PIOB3Enter or exit Manual Override modePIOB4RotatePIOB5RotateCounterclockwise

The rotations apply to the currently selected motor. Once the adjustments are complete, pressing *PIOB3* again will exit **Manual Override** and the solver will continue with the next move.

[1] Herbert Kociemba. Cube Explorer. http://kociemba.org/cube.htm, 2006.

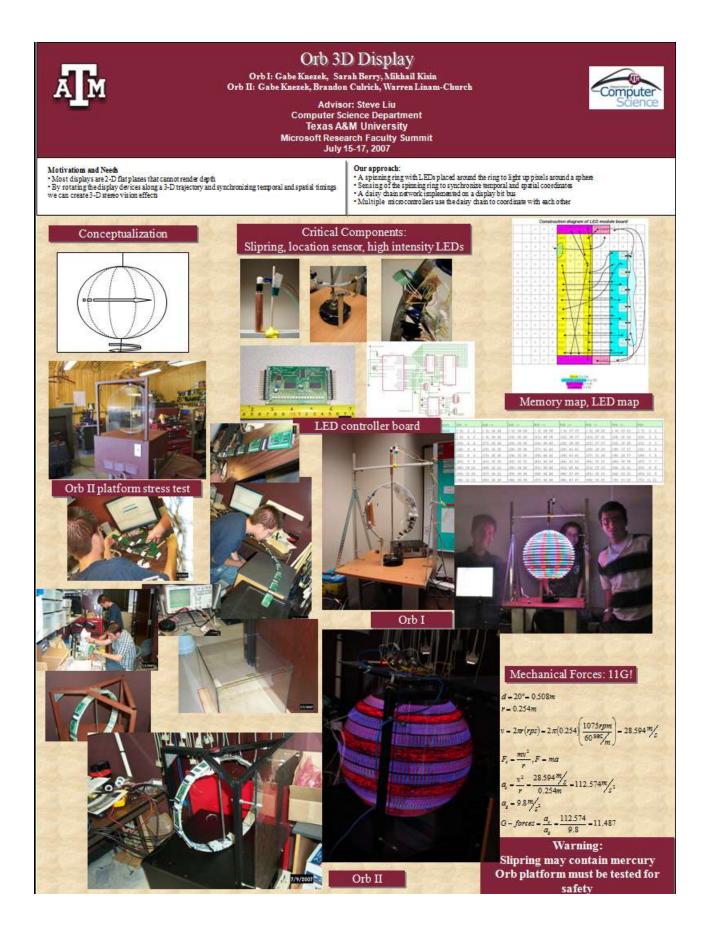

# **Orb Spherical Display**

## Sarah Berry, Brandon Culrich, Mikhail Kisin, Gabe Knezek, Warren Linam-Church, Steve Liu *Texas A&M University*

## Abstract

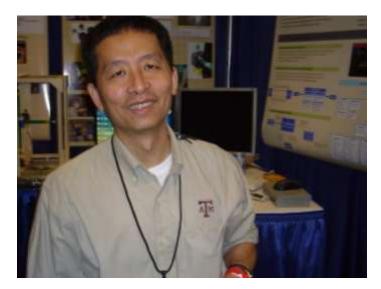

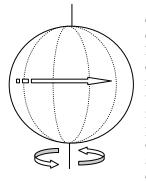

The Aggie Orb is a spherical display system capable of displaying images on a rotational ring, which rotates at a speed of 1100 RPM (corresponding to approximately 20fps) to create the spherical visual effects. This project represents two generations of development efforts by undergraduate students in the computer science department of the Texas A&M University. The first generation Orb I was a light-weight prototype built using hand-made circuit boards, connectors, and pedestal. The success of Orb I led to the creation of Orb II, which was built on a heavy duty metal frame and pedestal, a Plexiglas safety enclosure, twelve custom-built LED controller modules connected in a daisy chain, and a high performance slip ring to implement the spherical display concept. Due to the heavy weight (over 200 pounds) and large size, two students loaded the artifact on a van and drove for three days from College Station, TX to Redmond, WA to present the project results at the Summit.

## 1 Introduction

The Orb II project is an extension of the Global Spinomatic 3000 project (Orb I) created by Sarah Berry, Mikhail Kisin, and Gabe Knezek in the CPSC 462 Microcomputer Systems course. Given the time allotted (about 1 month) and the budget constraints, the Orb I was an excellent proof of concept with regard to spherical rendering. At completion of the semester the students were invited to extend the project with higher grade material, more advanced manufacturing processes, and more advanced computing and communication architectures. Some students in the Orb I project chose not to continue the endeavor, and two new students joined the continuation project. Orb I was implemented in a class setting within a planned schedule, whereas Orb II was implemented in a small group, under the direct supervision of the instructor and under a directed study class code.

## 2 Cyber-physical system principles

The problem space of the spherical display idea is the synchronization of the temporal and spatial activities in the cyber and physical dimensions. It went through three generations of testing in an integrated teaching and research environment before it was formalized into the lab exercises of the class. The first generation product (shown at side) is an air banner controlled by a PIC processor and capable of visualizing characters input from the PC. This project was mentioned at DemoFest'04 in the Embedded Systems education panel.

The second generation prototype is a laser pointer writer, designed to plot graphs on the wall using the combined

motions of a laser pointer and a mirror controlled by stepper motors. The controlling software runs on the EB63 evaluation board. The Microsoft Invisible Computing runtime provides the resource management services and real time management functions for the display system. The pictures show the prototype as well as its projected output on a dark background. The laser display system was first reported at DemoFest'05 in the Embedded Systems education panel.

The idea of using laser pointer and mirror to demonstrate the temporal and spatial synchronization appeared to be a cost-effective approach for the undergraduate microprocessor class. A new version of the basic design based on servo motors was created and further expanded into a dual platform system.

A gyro chip was used to realize an additional an input command device that allows the interactive control of the drawings. This prototype was demonstrated at DemoFest'06. At this point, the concept was mature enough to be formalized into a series of lab exercises for students to learn the basic principles of temporal and spatial

synchronization through prototyping. It proved a highly effective platform for students to understand the issues in the cyber (temporal) and physical (motion) synchronization. The Orb system therefore is only the latest result in a long thread of evolution.

## **3** System concept and the Orb architecture

The Orb architecture is based on a single-axis mechanical structure. All the electronic parts are integrated into a spinning ring; the visual effects are generated by multicolor LEDs moving along a spherical trajectory at a rate high enough to be undetectable to the human eye (approx 15-20 fps). A stationary magnet is placed near the spinning ring, and its coupling with a Hall Effect sensor placed on the ring itself indicates the current angle of the ring (latitude) to the controlling software. Using the latitude information, software controls the timing and color of the LEDs to create the pseudo-stationary patterns. Effectively, while in motion the device creates a sphere of "pixels" usable to display color images. The number of pixels in the vertical dimension (longitude) is statically defined by the number of LEDs placed on the ring. Notice that it is possible to alternate LEDs from the two sides of the ring to obtain a finer resolution in this dimension. Software could conceivably reduce the resolution by darkening alternating rows of LEDs. The number of pixels in the horizontal dimension

(latitude) is instead dynamically defined only by software, but in reality it is limited by the maximum switching rate of the LEDs (at the pole).

The Orb I used a centralized computing architecture to control a small number of high intensity LEDs directly placed into a small aluminum ring, and all the control circuits were hand made, physically bounded on the ring with hot glue.

The Orb II has a steel beam based mechanical frame, which was tested by running it for an hour of constant high-speed rotation to ensure that the mechanical strength is adequate. A total of 12 LED-controlling modules based on high intensity LEDs, LED drivers and AVR microcontrollers were designed and fabricated for the spherical illumination system. Each of the 12 LED modules is equipped with 18 tri-color LEDs. The modules are interconnected via a daisy chain bus to transfer data and power to all the modules on the ring, and to the external computing system outside the ring. The image resolution is 100x162 pixels. The off-ring computing system is interfaced to the on-ring LED modules through a six-lead slip ring. Each pair of matching leads on the slip ring provides the continuous connectivity while the slip ring is spinning.

## 4 Mechanical design and safety considerations

After the mechanical structure passed the stress test, all cables and their connectors, the microcontroller boards for the LED displays, the communications and other supporting functions were realized and tested off-line. The daisy chain bus successfully passed the functional test the very first time when the LED modules were powered up and interconnected. The most challenging issues are related to securing the modules to the ring so that parts do not get loose and fly out. After multiple tests, we found that the high strength fishing lines and Velcro tapes can indeed secure the boards, cables and their connectors under an estimated 11G of spinning force. For extra precaution, we added a transparent enclosure in Plexiglas that protects the spectators from catastrophic rupture events.

The quality of the visual effect improves with a higher spinning rate, but this also leads to stronger structural vibrations. Great care must be taken to balance the weight distributions to avoid potentially severe property damage or even injuries. The spinning generates considerable lateral forces; see below the G force calculations for the ring.

## 5 The journey

The plan was to demonstrate the Orb II and two other projects at the DemoFest'07 event, but the deadline approached and the project infact was far from complete. Because of its heavy weight (estimated over 200 *lbs*) and its large size, transport of the Orb II is not trivial. We inquired multiple carriers of their time and other delivery restrictions. It was concluded that the lead time, packaging and shipping could become a major hurdle to the plan. Eventually Gabe Knezek and Warren Linam-Church decided to simply rent a minivan and embark in the three days road trip from College Station, TX to deliver the prototype and development computers to Redmond, WA. Their GPS location was relied to the instructor and other collaborators, who followed Gabe and Warren until their safe arrival.

#### 6 The demo

The prototype was tested for low bandwidth communications through the slip ring but the powerful spinning motor caused significant noise on the DC power and communication links. The image mapping software, whose original function was to drive the Orb display patterns in real time, was instead used to transform any image into the display format of the spherical surface. The most popular pattern used in the demo is the planar earth, as shown in the short movie in Appendix B. It took a few seconds for the motor to reach its table speed, and also for the software system to calibrate to its average readings. A short movie illustrating the Orb in action is shown in Appendix B. The spherical display shows the Earth, using a bitmap taken from the Windows time-zone applet and downloaded in advance to the microcontrollers.

## 7 Operations

Currently, the LED modules are powered by eight rechargeable batteries, which should be fully charged before a demo session. The batteries are located at the bottom of the ring and need to be securely placed in their casing, with all the flat cables tugged in over them. The protective cage and the front cover must be tightened before the motor power is turned on. The prototype is not designed for long time of continuous operation. If the noise increases (loosening of screws on the cover), odd smell emerges (overheated motor) the power should be shut down immediately.

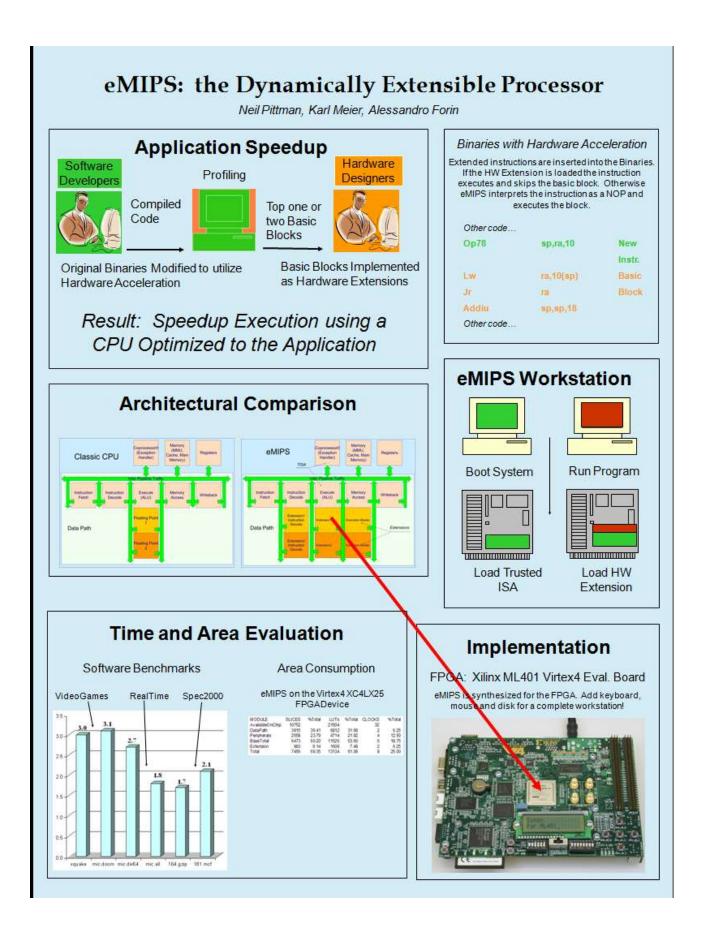

## **eMIPS** Prototype Introduction

## Richard Neil Pittman, Alessandro Forin Microsoft Research

#### Abstract

The eMIPS architecture is able to realize the performance benefits of application-specific hardware optimizations in a general-purpose, multi-user system environment using a dynamically extensible processor architecture. It allows multiple secure Extensions to load dynamically and to plug into the stages of a pipelined data path, thereby extending the core instruction set of the microprocessor. Extensions can also be used to realize on-chip peripherals and if area permits even multiple cores. The first eMIPS prototype is implemented on a Xilinx ML401 development board for the Virtex-4 XC4LX25 FPGA. A working prototype was introduced for the first time to the academic community at the Microsoft Faculty Summit in July 2007. Practical demonstrations included executing the hardware validation tests, a simple program demonstrating the new functionality provided by the architecture, and an HTTP server running on top of an embedded RTOS.

#### **1** Introduction

The eMIPS dynamically extensible processor implements the MIPS RISC architecture, augmented with hardware Extensions that are dynamically loaded and can interact directly with the RISC pipelined data path. The eMIPS processor prototype is implemented on a Xilinx Virtex 4 LX25 device (XC4LX25) integrated in a Xilinx ML401 development board. The partial reconfiguration feature available on Xilinx Virtex FPGAs makes it possible for the eMIPS processor to change dynamically the level of performance or functionality to adapt to the changing needs of its applications. In the first part of the demonstration, we used the hardware validation tests and an automated test driver to run a number simple programs. For each program, the processor is reset, the program is downloaded to RAM over a serial line connection by the on-chip bootloader, control is transferred to the program and the pass/fail state of the test is detected by capturing its output to the serial line. These tests verify the proper functioning of the processor itself and of the on-chip peripherals; they are used by the eMIPS developers to verify any changes they make before they attempt to load a full OS.

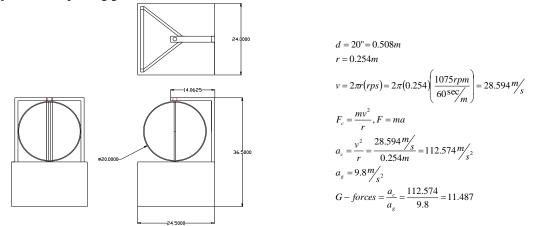

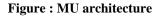

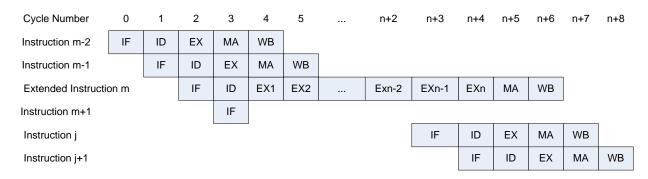

In the second part of the demonstration, we booted a small embedded operating system and ran a test using the first practical Extension that was developed. This Extension is used to accelerate (a portion of) a software-implemented 64-bit division using 32-bit arithmetic. The intermediate step in the division is shown below in MIPS assembly. It involves shifting 128-bit quantities across four 32-bit registers, comparing two 128-bit values, 128-bit subtraction and 32-bit OR to raise a quotient bit if necessary.

| sll  | r1,r1,1  |

|------|----------|

| srl  | r3,r2,31 |

| or   | r1,r1,r3 |

| sll  | r2,r2,1  |

| srl  | r3,r4,31 |

| or   | r2,r2,r3 |

| sll  | r4,r4,1  |

| srl  | r3,r5,31 |

| or   | r4,r4,r3 |

| sltu | r3,r1,r6 |

| beq  | r0,r3,40 |

| sll  | r5,r5,1  |

The Extension targets this 128-bit shift-by-one in the division process. Shifting a bus by a single bit is a trivial task for hardware but the software is forced to work with 32-bit registers at a time. This requires shifting one register by one, getting the most significant bit of the next register by shifting it, OR the shifted register with the most significant bit of next register and repeat. The Extension is able to read four registers from the register file, input them into a shift register, perform the shift by one and write the registers back. This is illustrated in the figure below.

The Extension also performs a conditional jump, as indicated by the last three MIPS instruction in the block above. The Extension compares the value of R1 with another register R6 (not in the figure) and based on that comparison the Extension either updates the PC before relinquishing control or it allows the flow to fall through to the current next instruction.

We demonstrated the division Extension using a test program called "mmldiv64\_ext.exe" and using the Microsoft Invisible Computing Embedded Operating System. The picture below shows the output captured from a PC. In the first attempt to execute the program the Extension is not loaded, which results in the program attempting to execute an Extended instruction which is not recognized by the processor. This results in a Reserved Instruction exception that is captured by the OS handler, which then dumps the content of the processor registers and terminates the program.

In the next step, we use the XILINX iMPACT tool to load the Extension over the JTAG cable, and the test program this time runs successfully to completion. The same set of 64-bit divisions are executed (and the results checked) in three different ways by the test. The first time they are executed by the original version of the 64-bit division and timed using the on-chip 10MHz free-running counter. The second time we execute the modified version of the 64-bit division, which differs from the previous one only in the insertion of the Extended instruction at the start of the suindicated basic block. For timing purposes, the first time around we nullify this instruction, e.g. we treat it as a NOP instruction. In the third and final pass we do recognize the Extended instruction and execute the basic block directly in the Extension. The test then compares the timings for the three runs and prints the speedups that were obtained.

| 📾 Visual Studio 2005 Command Prompt - serplexd -n -s                                                                                                                                 |                |             | - 8 × |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------|

| MARK - RUNNING BASELINE<br>READY<br>SET<br>Go!!!                                                                                                                                     |                |             | -     |

| TRAP 32808 (1200ff14) Context=80021f90<br>Context is [<br>00000000 00000000 00000000 00000000<br>fffrc88a 80000000 00000000 649f0000<br>00000000 00000000 00000000 0000000<br>000000 |                |             |       |

| MARK - RUNNING NON EXTENSION TEST<br>READY<br>Set<br>GO?!?                                                                                                                           |                |             |       |

| DONE<br>MARK - RUNNING BASELINE<br>READY<br>SET<br>GO?!!                                                                                                                             |                |             |       |

| DONE<br>Mark - Running Extension test<br>Ready<br>Set<br>Gofff                                                                                                                       |                |             |       |

| DONE                                                                                                                                                                                 |                |             |       |

| RESULTS                                                                                                                                                                              |                |             |       |

| Errors = 0<br>NON EXTENSION TEST RESULTS<br>NOEXT START = 0. 8a2e2<br>NOEXT FINISH = 0. 31dfe66<br>NOEXT TIME = 3155b84                                                              |                |             |       |

| BASELINE RESULTS<br>BASE START = 0. 328bdbb<br>BASE FINISH = 0. 66a05a9<br>BASE TIME = 34147ee                                                                                       |                |             |       |

| EXTENSION TEST RESULTS<br>EXT START = 0.6758de2<br>EXT FINISH = 0.7d78d4f<br>EXT TIME = 161ff6d                                                                                      |                |             |       |

| PERFORMANCE over base (base/ext) =<br>PERFORMANCE over original (noext/ext) =<br>OUERHEAD over original (base/noext) =<br>TEST PASSED SUCCESSFULLY<br>>                              | 2.<br>2.<br>1. | 3<br>2<br>0 | T     |

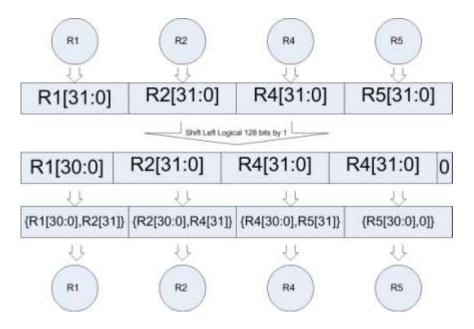

The system has now become stable enough to execute a more complex test, involving the same embedded operating system as above but using more complex software and a more diverse set of peripherals. As shown in the figure below, we can access the FAT16 file system on the ML401 Compact Flash card and list its content by talking to a simple command interpreter. We can then execute a script to start the network protocol stack, which communicates to the corporate Ethernet using the same serial line and relaying packets using the VirtualPC NIC driver. As shown in the figure, the system uses the DHCP protocol to acquire an IP address for itself, and the IP addresses of the DNS servers.

We then start a Web server service as the last command in the picture.

| 🐱 Visual Studio 2005 Command Prompt - serplexd -s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - 🗆 × |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Setting environment for using Microsoft Visual Studio 2005 x86 tools.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| Satting environment for using Microsoft Visual Studie 2005 x86 tools.<br>E:\PFGA:eMIPS\fpga_side\data>serplexd -s<br>Vill talk to a BigEndian client (mips.ppc)<br>Console Thread<br>CPTO-3<br>> dir fat<br>Md4.htm<br>arrow.gif<br>contents.htm<br>hasge81 hap<br>inage82.bap<br>inage85.bap<br>inage85.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage87.bap<br>inage8.bap<br>inage87.bap<br>inage8.bap<br>inage87.bap<br>inage8.bap<br>inage87.bap<br>inage87.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8.bap<br>inage8. |       |

| 157.54.14.178<br>157.54.14.162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| The domain name on this interface is 'redmond.corp.microsoft.com'<br>> http.cob                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

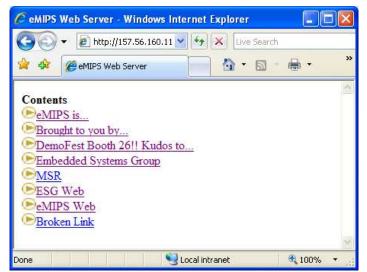

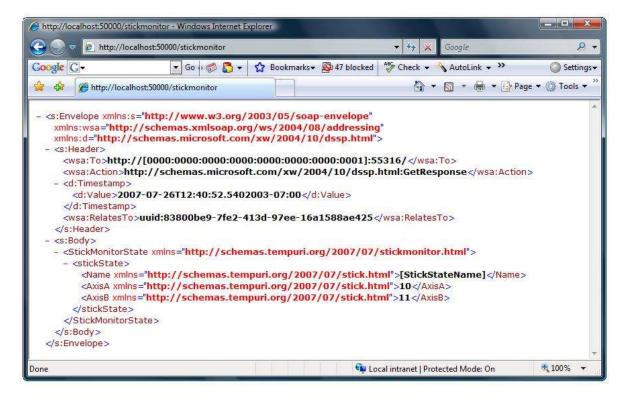

Moving to a separate PC, we can start a web browser and point to the IP address of the ML401 board, resulting in the following output.

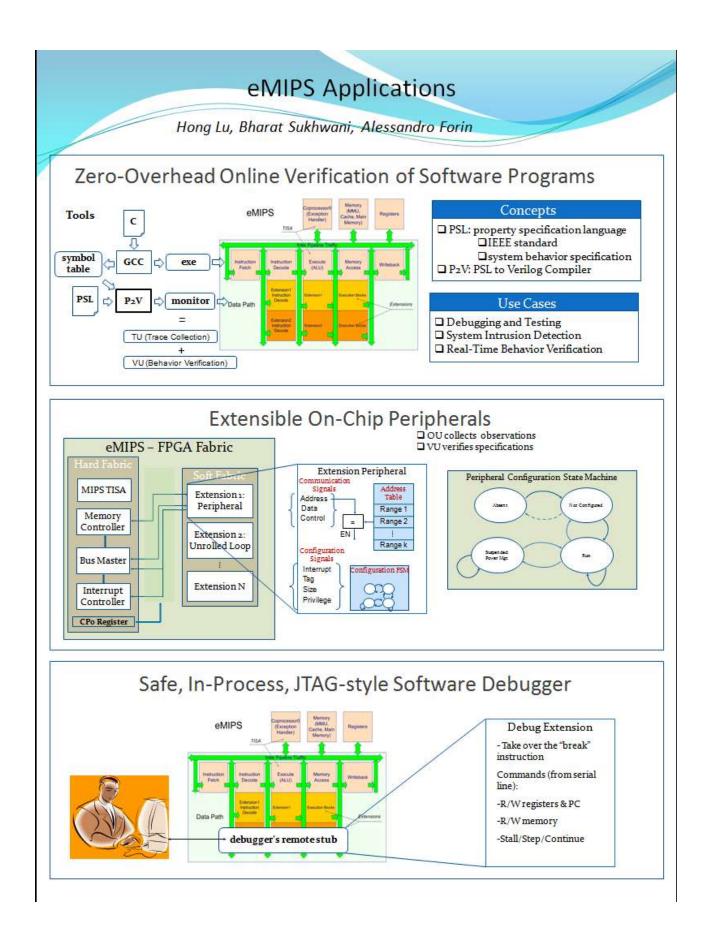

## **Extensible Peripherals for eMIPS**

Bharat Sukhwani Boston University

Richard Neil Pittman, Alessandro Forin Microsoft Research

#### Abstract

The area limitations of the XC4LX25 device on which eMIPS is implemented have spurred innovative solutions in the I/O peripherals support. Rather than permanently devoting area resources to the peripherals in the core section of the microcomputer (the TISA), eMIPS peripherals can be allocated to the extension area and loaded and unloaded dynamically, as required by the software application. At the summit we demonstrated the overall scheme in action by loading and unloading a timer under software control. The demonstration was performed using the Giano simulator. We also showed the progress already made towards implementing this functionality on the XC4LX25 by means of a simple extension that makes use of the additional privileged interface signals that are required for I/O peripherals to access interrupts and physical memory, to be configured into the system memory map, all the while maintaining the security and trust levels of the core TISA module.

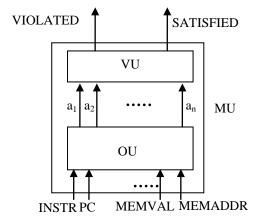

#### 1 Introduction

Dynamic loading and unloading of on-chip peripherals is performed by the system software using the extension slots in the eMIPS processor. System software initiates the loading of the extension peripheral by sending a signal to the Xilinx System Ace FPGA control chip, which in turn loads the corresponding bit file for the extension into the "soft fabric" of the reconfigurable hardware (Appendix A:Poster 5). The extension then sends an interrupt signal to the on-chip Bus Master (on the "hard fabric") to indicate that it needs to be configured. The Bus Master acts as a bridge between the extension peripheral and the memory controller and is used to configure the extension peripheral. All the resources requested by the peripheral (including the interrupt request, if any) are passed to the memory controller via the Bus Master. When the peripheral is configured it communicates directly with the memory controller, bypassing the Bus Master. Once the system software is finished using the peripheral, it can unload it, freeing up both the portion of the memory address space used by the peripheral as well as the reconfigurable extension slot which can then be reused by another extension.

#### 2 Demonstrations

#### 2.1 Load and Unload Simulation

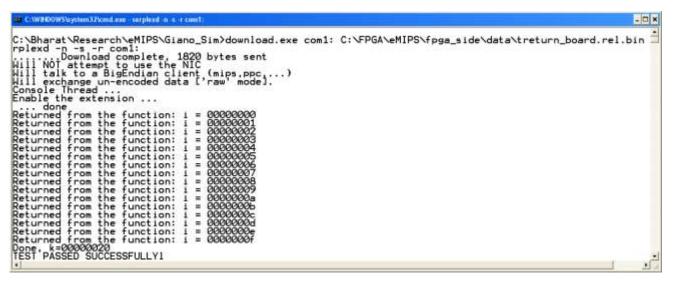

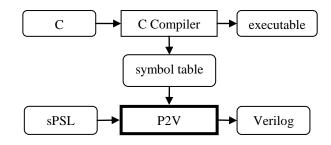

Our first demonstration presented the overall plan for extensible on-chip peripherals. We presented a test performing the processes of loading an extension peripheral and then unloading it. The software program "pload" was compiled for eMIPS and then executed on the Giano simulator, configured for the ML401 board.

The Giano simulation of the eMIPS processor is started by executing the following command

```

> giano.exe -Platform Ml401.plx GPIO::ValueAtReset 0

```

```

Emachage State Stat

```

#### Figure

Here, giano.exe is the executable for the Giano simulator, and the file. Ml401.plx represents the eMIPS system and contains block level representations of the different modules (baseline processor, memory module, memory bus, extensions, peripherals etc.); each block in turn corresponding to a .dll file that implements the functionality of that block. The ValueAtReset attribute sets the values of the GPIO pins on the board to zero, which indicates to the boot loader that it should download executable code from the serial line, rather than jumping directly to the code in the on-board FLASH. Figure 1 shows the output on the command window after running the above command.

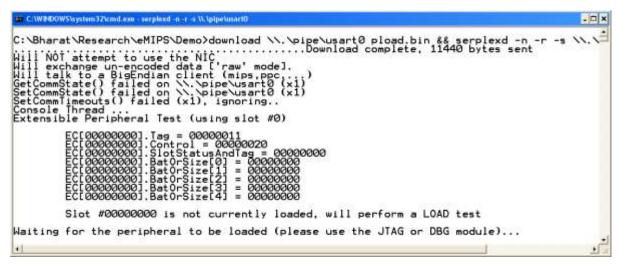

Once Giano is started the eMIPS boot loader waits for the software program to be downloaded, which is done using the following command:

```

> download \\.\pipe\usart0 pload.bin && serplexd -n -r -s \\.\pipe\usart0

```

The corresponding command window is shown in Figure 2

#### Figure

**Pload.bin** is the software test program used to perform the loading/unloading of peripherals using extension slot number 0. If the program finds that the peripheral is not loaded, it performs the peripheral load test otherwise it unloads the peripheral. The screenshot of Figure 2 shows that the program initially finds that there is no peripheral loaded in extension slot 0, and the program therefore proceeds with the load test.

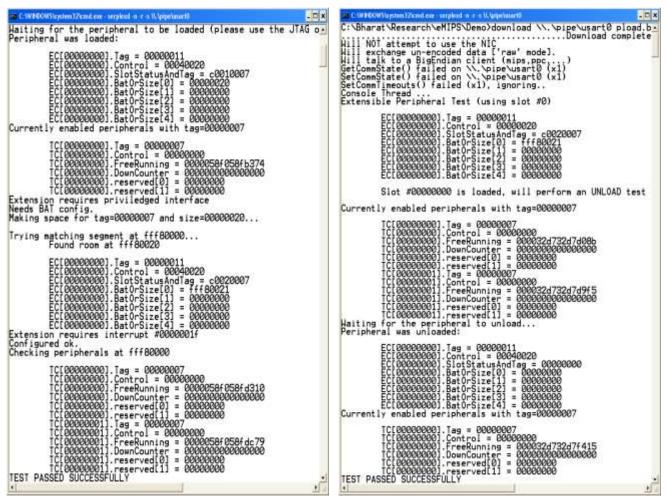

When an extension peripheral is loaded, the Extension Controller (EC) receives an indication (from the extension) as to the presence of an extension in slot 0. The EC in turn raises an interrupt signal to indicate to the system software that the peripheral needs to be configured. In the current demo, we pass an input "11 0" to the debug module inside the Giano simulator (previous command window, Figure 1) to simulate the hardware indication, so that the software program can then continue with the configuration of the peripheral. Once EC receives this input, the PLOAD program starts the actual

Figure

Figure

configuration process.

Figure 3 shows the output from PLOAD during the extension load test. The program initially prints the contents of the registers of the EC and TC peripherals. EC represents the extension controller and is used to control the configuration of the extension peripheral. TC represents the Timer Controller, which is the type of extension peripheral being configured in this demonstration. As shown in the figure, once the peripheral is loaded PLOAD looks at the EC state to identify the resources required. The SlotStatusAndTag register shows that the peripheral has a tag 7 (which classifies it at a Timer) and requests privileged access as well as interrupts. The BatOrSize [0] register shows that the peripheral requires 32 bytes of address space. The memory controller first checks if a peripheral with the same tag already exist, and if so, it tries to allocate space for the new peripheral at a memory address contiguous to the existing peripheral. In the present test, a timer peripheral already exists (TC [0] in Figure 3) and hence PLOAD maps the new timer to a location next to the current one. To do this, software updates the BatOrSize [0] register of the EC to indicate that the starting address of the extension peripheral is address 0xfff80020, with the valid bit (least significant bit) set to 1. PLOAD then moves the peripheral to the "Run" state and configuration is complete. The test finally indicates that it passed successfully and the memory map indicates now two timer controllers TC [0] and TC [1].