Technical information

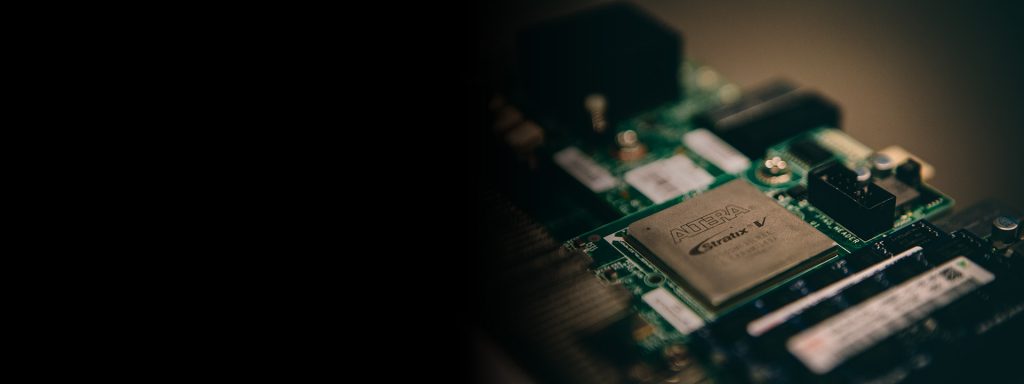

The system consists of 384 2-socket Intel Xeon-based nodes, each with 64 GB of RAM and an Altera Stratix V FPGA with 8 GB of local DDR3 SDRAM. FPGAs communicate to their host CPUs via a PCIe Gen3 x8 connection, providing 8 GB/s guaranteed-not-to-exceed bandwidth, and each FPGA can read and write data stored on its host node using this connection.

The FPGAs are connected to one another via a dedicated network using high-speed serial links. This network, called CatNet (Catapult Network), forms a two-dimensional torus within a pod of 48 servers and provides low-latency communication between neighboring FPGAs. This design supports the use of multiple FPGAs to solve a single problem while adding resilience to server and FPGA failures.

Per Node:

- Two Xeon E5-2450, 2.1 GHz, 8-core, 20 MB Cache, 95W

- 64 GB of RAM

- Four 2 TB 7.2k 3G SATA 3.5″; two 480 GB 6G Micron SATA SSD 2.5

- Intel 82599 10GbE Mezz Card

- Altera Stratix V FPGA Card

- Operating system: Windows Server 2012